Part Number: AM625-Q1

Other Parts Discussed in Thread: AM62P, AM625

Tool/software:

Hi Team,

We have custom board with OLDI port 0 output for Display 800x480 .

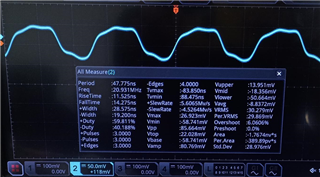

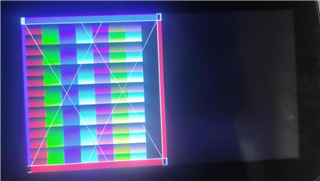

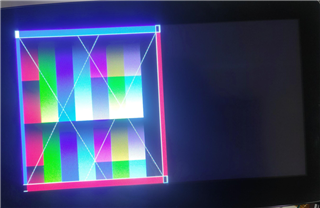

when i use 800x480 timing i get half display . Height seems fine . Width has issues

static const struct drm_display_mode custom_mode = {

.clock = 24750,

.hdisplay = 800,

.hsync_start = 800 + 54,

.hsync_end = 800 + 54 + 2,

.htotal = 800 + 54 + 2 + 44,

.vdisplay = 480,

.vsync_start = 480 + 49,

.vsync_end = 480 + 49 + 2,

.vtotal = 480 + 49 + 2 + 22,

};

static const struct panel_desc custom = {

.modes = &custom_mode,

.num_modes = 1,

.bpc = 8,

.size = {

.width = 152,

.height = 91,

},

.delay = {

.prepare = 50,

.disable = 50,

},

.bus_flags = DRM_BUS_FLAG_DE_HIGH,

.bus_format = MEDIA_BUS_FMT_RGB888_1X7X4_JEIDA,

.connector_type = DRM_MODE_CONNECTOR_LVDS,

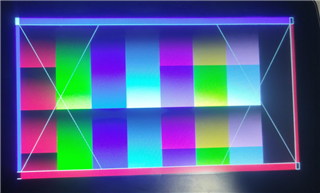

};but when i use 1600x480 , it display full 800x480 but Unfortunately modetest get 1600x480 so, the GUI we did for 800x480 is collapsed.

static const struct drm_display_mode custom_mode = {

.clock = 49500,

.hdisplay = 1600,

.hsync_start = 1600 + 54,

.hsync_end = 1600 + 54 + 2,

.htotal = 1600 + 54 + 2 + 44,

.vdisplay = 480,

.vsync_start = 480 + 49,

.vsync_end = 480 + 49 + 2,

.vtotal = 480 + 49 + 2 + 22,

};

static const struct panel_desc custom = {

.modes = &custom_mode,

.num_modes = 1,

.bpc = 8,

.size = {

.width = 152,

.height = 91,

},

.delay = {

.prepare = 50,

.disable = 50,

},

.bus_flags = DRM_BUS_FLAG_DE_HIGH,

.bus_format = MEDIA_BUS_FMT_RGB888_1X7X4_JEIDA,

.connector_type = DRM_MODE_CONNECTOR_LVDS,

};

any idea why its happening?

this is the overlay we use FYR

// SPDX-License-Identifier: GPL-2.0-or-later OR MIT

/**

* Microtips integrated OLDI panel (MF-101HIEBCAF0) and touch DT overlay for AM625 - SK

*

* Copyright (C) 2024 Texas Instruments Incorporated - http://www.ti.com/

*/

/dts-v1/;

/plugin/;

#include <dt-bindings/gpio/gpio.h>

#include <dt-bindings/interrupt-controller/irq.h>

#include "k3-pinctrl.h"

&{/} {

display {

compatible ="custom";

port@0 {

dual-lvds-odd-pixels;

lcd_in0: endpoint {

remote-endpoint = <&oldi_out0>;

};

};

};

hdmi0: connector {

status = "disabled";

};

};

&dss {

status = "okay";

};

&main_pmx0 {

main_oldi0_pins_default: main-oldi0-pins-default {

pinctrl-single,pins = <

AM62X_IOPAD(0x0260, PIN_OUTPUT, 0) /* (AA5) OLDI0_A0N */

AM62X_IOPAD(0x025c, PIN_OUTPUT, 0) /* (Y6) OLDI0_A0P */

AM62X_IOPAD(0x0268, PIN_OUTPUT, 0) /* (AD3) OLDI0_A1N */

AM62X_IOPAD(0x0264, PIN_OUTPUT, 0) /* (AB4) OLDI0_A1P */

AM62X_IOPAD(0x0270, PIN_OUTPUT, 0) /* (Y8) OLDI0_A2N */

AM62X_IOPAD(0x026c, PIN_OUTPUT, 0) /* (AA8) OLDI0_A2P */

AM62X_IOPAD(0x0278, PIN_OUTPUT, 0) /* (AB6) OLDI0_A3N */

AM62X_IOPAD(0x0274, PIN_OUTPUT, 0) /* (AA7) OLDI0_A3P */

AM62X_IOPAD(0x0280, PIN_OUTPUT, 0) /* (AC6) OLDI0_A4N */

AM62X_IOPAD(0x027c, PIN_OUTPUT, 0) /* (AC5) OLDI0_A4P */

AM62X_IOPAD(0x0288, PIN_OUTPUT, 0) /* (AE5) OLDI0_A5N */

AM62X_IOPAD(0x0284, PIN_OUTPUT, 0) /* (AD6) OLDI0_A5P */

AM62X_IOPAD(0x0290, PIN_OUTPUT, 0) /* (AE6) OLDI0_A6N */

AM62X_IOPAD(0x028c, PIN_OUTPUT, 0) /* (AD7) OLDI0_A6P */

AM62X_IOPAD(0x0298, PIN_OUTPUT, 0) /* (AD8) OLDI0_A7N */

AM62X_IOPAD(0x0294, PIN_OUTPUT, 0) /* (AE7) OLDI0_A7P */

AM62X_IOPAD(0x02a0, PIN_OUTPUT, 0) /* (AD4) OLDI0_CLK0N */

AM62X_IOPAD(0x029c, PIN_OUTPUT, 0) /* (AE3) OLDI0_CLK0P */

AM62X_IOPAD(0x02a8, PIN_OUTPUT, 0) /* (AE4) OLDI0_CLK1N */

AM62X_IOPAD(0x02a4, PIN_OUTPUT, 0) /* (AD5) OLDI0_CLK1P */

>;

};

};

&dss {

pinctrl-names = "default";

pinctrl-0 = <&main_oldi0_pins_default &main_dss0_pins_default>;

};

&dss_ports {

#address-cells = <1>;

#size-cells = <0>;

/* VP1: Output to OLDI */

port@0 {

reg = <0>;

oldi_out0: endpoint {

remote-endpoint = <&lcd_in0>;

};

};

port@1 {

status = "disabled";

};

};

&main_i2c1 {

sii9022: sii9022@3b {

status = "disabled";

};

};