Tool/software:

Hello,

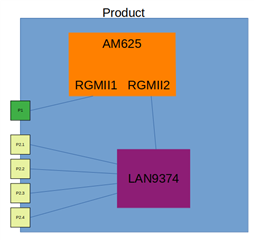

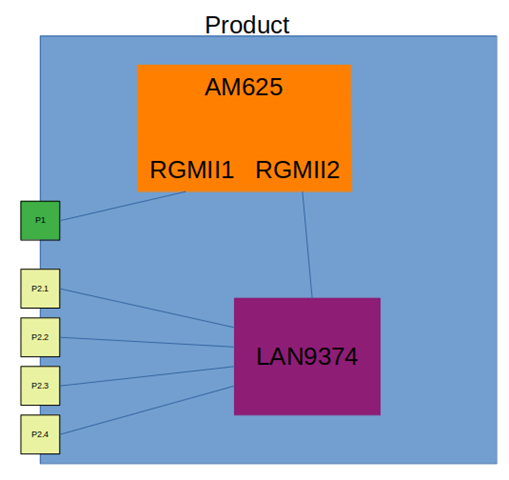

I am trying to to connect an Ethernet switch to the RGMII2 interface on the AM625. The switch in question is a Microchip LAN8374.

The issue I'm having is with being able to connect the switch RGMII port to the AM625's RGMII2 interface- specifically, I cannot link the `ethernet` property of the port node to the cpsw_port2 node as it causes the switch initialisation to fail (ultimately because it cannot find the master node). I can successfully initialise the switch if I connect it to the cpsw3g node, but this seems to connect it to the RGMII1 interface rather than RGMII2.

My device tree configuration for the CPSW peripherals is as follows:

&cpsw3g {

bootph-all;

pinctrl-names = "default";

status = "okay";

pinctrl-0 = <ðernettx_pins_default>, <ðernett1internalswitch_pins_default>;

fixed-link {

speed = <1000>;

full-duplex;

};

};

/* TX Ethernet */

&cpsw_port1 {

bootph-all;

phy-mode = "rmii";

phy-handle = <&cpsw3g_phy0>;

//ti,dual-emac-pvid = <1>;

status = "okay";

};

/* T1 Ethernet Switch */

&cpsw_port2 {

//phy-mode = "rgmii-id";

phy-mode = "rgmii";

#address-cells = <1>;

#size-cells = <0>;

//ti,dual-emac-pvid = <2>;

status = "okay";

fixed-link {

speed = <1000>;

full-duplex;

};

};

/* Ethernet MDIO */

&cpsw3g_mdio {

bootph-all;

status = "okay";

pinctrl-names = "default";

pinctrl-0 = <ðernetmdio_pins_default>;

cpsw3g_phy0: ethernet-phy@7 {

bootph-all;

reg = <7>;

rx-internal-delay-ps = <1>;

tx-internal-delay-ps = <1>;

};

};

And my switch configuration is:

lan9374: switch@0 {

compatible = "microchip,lan9374";

reg = <0>;

spi-max-frequency = <44000000>;

power-supply = <&p1v1>;

phy-mode = "rgmii-id";

status = "okay";

mdio {

#address-cells = <1>;

#size-cells = <0>;

t1phy2a: ethernet-phy@0{

reg = <0x0>;

};

t1phy2b: ethernet-phy@1{

reg = <0x1>;

};

t1phy2d: ethernet-phy@2{

reg = <0x2>;

};

t1phy2f: ethernet-phy@3{

reg = <0x3>;

};

t1phy2e: ethernet-phy@6{

reg = <0x6>;

};

t1phy2c: ethernet-phy@7{

reg = <0x7>;

};

};

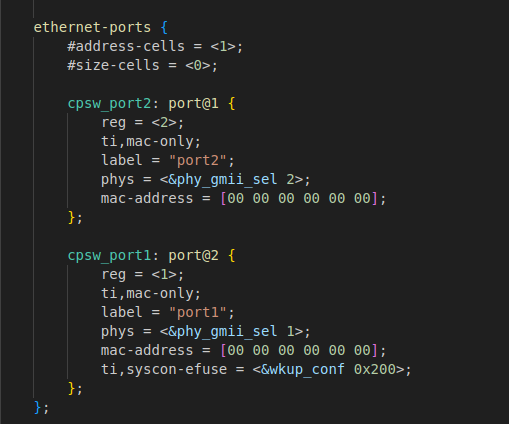

ethernet-ports {

#address-cells = <1>;

#size-cells = <0>;

port@0 {

reg = <0>;

label = "t1port2a";

phy-mode = "internal";

phy-handle = <&t1phy2a>;

};

port@1 {

reg = <1>;

label = "t1port2b";

phy-mode = "internal";

phy-handle = <&t1phy2b>;

};

port@2 {

reg = <2>;

label = "t1port2d";

phy-mode = "internal";

phy-handle = <&t1phy2d>;

};

port@3 {

reg = <3>;

label = "t1port2f";

phy-mode = "internal";

phy-handle = <&t1phy2f>;

};

port@4 {

reg = <4>;

label = "othermicro";

phy-mode = "rmii";

tx-internal-delay-ps = <2000>;

rx-internal-delay-ps = <2000>;

fixed-link {

speed = <100>;

full-duplex;

};

};

/* Link to AM625 */

port@5 {

reg = <5>;

label = "cpu";

phy-mode = "rgmii-id";

tx-internal-delay-ps = <2000>;

rx-internal-delay-ps = <2000>;

//ethernet = <&cpsw_port2>;

ethernet = <&cpsw3g>;

fixed-link {

speed = <1000>;

full-duplex;

};

};

port@6 {

reg = <6>;

label = "t1port2e";

phy-mode = "internal";

phy-handle = <&t1phy2e>;

};

port@7 {

reg = <7>;

label = "t1port2c";

phy-mode = "internal";

phy-handle = <&t1phy2c>;

};

};

};

Can you advise how DSA switches are supposed to be connected to RGMII2 please?

Thanks,

Ben