Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

Hi,

We are using Ethernet Port2 with a LAN9374 Switch connected. We are enable DSA drivers in the menuconfig.

While bootup we are able to detect the LAN9374, switch but we are getting deferred probing and no additional LAN ports from the switch are detected.

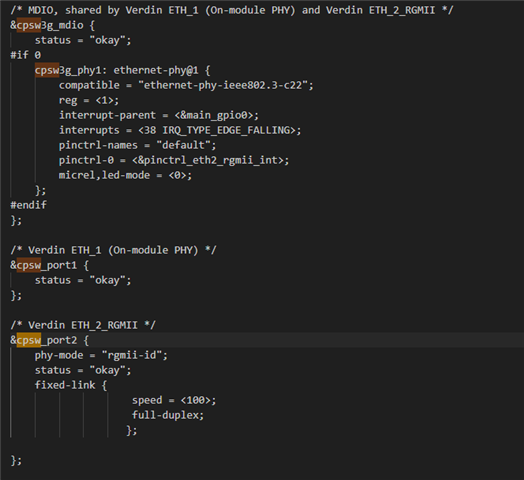

Below is the device tree,

/* Verdin ETH_2_RGMII */

&cpsw_port2 {

phy-handle = <&cpsw3g_phy1>;

phy-mode = "rgmii-rxid";

status = "okay";

fixed-link {

speed = <1000>;

full-duplex;

};

};

lan9374: switch@1 {

compatible = "microchip,lan9374";

spi-cpha;

spi-cpol;

reg = <1>;

spi-max-frequency = <2000000>;

ethernet-ports {

#address-cells = <1>;

#size-cells = <0>;

port@0 {

reg = <0>;

label = "lan1";

phy-mode = "internal";

phy-handle = <&t1phy0>;

};

port@1 {

reg = <1>;

label = "lan2";

phy-mode = "internal";

phy-handle = <&t1phy1>;

};

port@2 {

reg = <2>;

label = "lan4";

phy-mode = "internal";

phy-handle = <&t1phy2>;

};

port@3 {

reg = <3>;

label = "lan6";

phy-mode = "internal";

phy-handle = <&t1phy3>;

};

port@4 {

reg = <4>;

phy-mode = "rgmii";

tx-internal-delay-ps = <2000>;

rx-internal-delay-ps = <2000>;

ethernet = <&cpsw_port2>;

fixed-link {

speed = <1000>;

full-duplex;

};

};

port@5 {

reg = <5>;

label = "lan7";

phy-mode = "rgmii";

tx-internal-delay-ps = <2000>;

rx-internal-delay-ps = <2000>;

fixed-link {

speed = <1000>;

full-duplex;

};

};

port@6 {

reg = <6>;

label = "lan5";

phy-mode = "internal";

phy-handle = <&t1phy6>;

};

port@7 {

reg = <7>;

label = "lan3";

phy-mode = "internal";

phy-handle = <&t1phy7>;

};

};

mdio {

#address-cells = <1>;

#size-cells = <0>;

t1phy0: ethernet-phy@0{

reg = <0x0>;

};

t1phy1: ethernet-phy@1{

reg = <0x1>;

};

t1phy2: ethernet-phy@2{

reg = <0x2>;

};

t1phy3: ethernet-phy@3{

reg = <0x3>;

};

t1phy6: ethernet-phy@6{

reg = <0x6>;

};

t1phy7: ethernet-phy@7{

reg = <0x7>;

};

};

};

below is the error we are getting,

[ 1.303053] davinci_mdio 8000f00.mdio: Configuring MDIO in manual mode [ 1.348558] davinci_mdio 8000f00.mdio: davinci mdio revision 9.7, bus freq 1000000 [ 1.758624] davinci_mdio 8000f00.mdio: Configuring MDIO in manual mode [ 1.804547] davinci_mdio 8000f00.mdio: davinci mdio revision 9.7, bus freq 1000000 [ 1.818383] mdio_bus 8000f00.mdio: MDIO device at address 7 is missing. [ 1.825049] davinci_mdio 8000f00.mdio: phy[0]: device 8000f00.mdio:00, driver TI DP83867 [ 12.314148] am65-cpsw-nuss 8000000.ethernet eth0: PHY [8000f00.mdio:00] driver [TI DP83867] (irq=359) root@verdin-am62-15415780:~# dmesg [ 0.000000] Booting Linux on physical CPU 0x0000000000 [0x410fd034] [ 0.000000] Linux version 6.1.80-6.7.0-devel+git.603f75dc931d (oe-user@oe-host) (aarch64-tdx-linux-gcc (GCC) 11.4.0, GNU ld (GNU Binutils) 2.38.20220708) #1 SMP PREEMPT Tue Dec 17 05:07:49 UTC 2024 [ 0.000000] Machine model: Toradex Verdin AM62 on Verdin Development Board [ 0.000000] earlycon: ns16550a0 at MMIO32 0x0000000002800000 (options '') [ 0.000000] printk: bootconsole [ns16550a0] enabled [ 0.000000] efi: UEFI not found. [ 0.000000] Reserved memory: created DMA memory pool at 0x000000009db00000, size 12 MiB [ 0.000000] OF: reserved mem: initialized node r5f-memory@9db00000, compatible id shared-dma-pool [ 0.000000] Zone ranges: [ 0.000000] DMA [mem 0x0000000080000000-0x00000000bfffffff] [ 0.000000] DMA32 empty [ 0.000000] Normal empty [ 0.000000] Movable zone start for each node [ 0.000000] Early memory node ranges [ 0.000000] node 0: [mem 0x0000000080000000-0x000000009dafffff] [ 0.000000] node 0: [mem 0x000000009db00000-0x000000009e6fffff] [ 0.000000] node 0: [mem 0x000000009e700000-0x000000009e77ffff] [ 0.000000] node 0: [mem 0x000000009e780000-0x000000009fffffff] [ 0.000000] node 0: [mem 0x00000000a0000000-0x00000000bfffffff] [ 0.000000] Initmem setup node 0 [mem 0x0000000080000000-0x00000000bfffffff] [ 0.000000] cma: Reserved 128 MiB at 0x00000000b6c00000 [ 0.000000] psci: probing for conduit method from DT. [ 0.000000] psci: PSCIv1.1 detected in firmware. [ 0.000000] psci: Using standard PSCI v0.2 function IDs [ 0.000000] psci: Trusted OS migration not required [ 0.000000] psci: SMC Calling Convention v1.4 [ 0.000000] percpu: Embedded 20 pages/cpu s41064 r8192 d32664 u81920 [ 0.000000] pcpu-alloc: s41064 r8192 d32664 u81920 alloc=20*4096 [ 0.000000] pcpu-alloc: [0] 0 [0] 1 [ 0.000000] Detected VIPT I-cache on CPU0 [ 0.000000] CPU features: detected: GIC system register CPU interface [ 0.000000] CPU features: detected: ARM erratum 845719 [ 0.000000] alternatives: applying boot alternatives [ 0.000000] Built 1 zonelists, mobility grouping on. Total pages: 258048 [ 0.000000] Kernel command line: root=PARTUUID=4f9aa08c-02 ro rootwait console=tty1 console=ttyS2,115200 consoleblank=0 earlycon=ns16550a,mmio32,0x02800000 [ 0.000000] Dentry cache hash table entries: 131072 (order: 8, 1048576 bytes, linear) [ 0.000000] Inode-cache hash table entries: 65536 (order: 7, 524288 bytes, linear) [ 0.000000] mem auto-init: stack:off, heap alloc:off, heap free:off [ 0.000000] Memory: 840012K/1048576K available (11456K kernel code, 1398K rwdata, 3964K rodata, 2240K init, 426K bss, 77492K reserved, 131072K cma-reserved) [ 0.000000] SLUB: HWalign=64, Order=0-3, MinObjects=0, CPUs=2, Nodes=1 [ 0.000000] rcu: Preemptible hierarchical RCU implementation. [ 0.000000] rcu: RCU event tracing is enabled. [ 0.000000] rcu: RCU restricting CPUs from NR_CPUS=256 to nr_cpu_ids=2. [ 0.000000] Trampoline variant of Tasks RCU enabled. [ 0.000000] Tracing variant of Tasks RCU enabled. [ 0.000000] rcu: RCU calculated value of scheduler-enlistment delay is 25 jiffies. [ 0.000000] rcu: Adjusting geometry for rcu_fanout_leaf=16, nr_cpu_ids=2 [ 0.000000] NR_IRQS: 64, nr_irqs: 64, preallocated irqs: 0 [ 0.000000] GICv3: GIC: Using split EOI/Deactivate mode [ 0.000000] GICv3: 256 SPIs implemented [ 0.000000] GICv3: 0 Extended SPIs implemented [ 0.000000] Root IRQ handler: gic_handle_irq [ 0.000000] GICv3: GICv3 features: 16 PPIs [ 0.000000] GICv3: CPU0: found redistributor 0 region 0:0x0000000001880000 [ 0.000000] ITS [mem 0x01820000-0x0182ffff] [ 0.000000] GIC: enabling workaround for ITS: Socionext Synquacer pre-ITS [ 0.000000] ITS@0x0000000001820000: Devices Table too large, reduce ids 20->19 [ 0.000000] ITS@0x0000000001820000: allocated 524288 Devices @80800000 (flat, esz 8, psz 64K, shr 0) [ 0.000000] ITS: using cache flushing for cmd queue [ 0.000000] GICv3: using LPI property table @0x0000000080030000 [ 0.000000] GIC: using cache flushing for LPI property table [ 0.000000] GICv3: CPU0: using allocated LPI pending table @0x0000000080040000 [ 0.000000] rcu: srcu_init: Setting srcu_struct sizes based on contention. [ 0.000000] arch_timer: cp15 timer(s) running at 200.00MHz (phys). [ 0.000000] clocksource: arch_sys_counter: mask: 0x3ffffffffffffff max_cycles: 0x2e2049d3e8, max_idle_ns: 440795210634 ns [ 0.000001] sched_clock: 58 bits at 200MHz, resolution 5ns, wraps every 4398046511102ns [ 0.008630] Console: colour dummy device 80x25 [ 0.013656] printk: console [tty1] enabled [ 0.017902] Calibrating delay loop (skipped), value calculated using timer frequency.. 400.00 BogoMIPS (lpj=800000) [ 0.028599] pid_max: default: 32768 minimum: 301 [ 0.033378] LSM: Security Framework initializing [ 0.038251] Mount-cache hash table entries: 2048 (order: 2, 16384 bytes, linear) [ 0.045839] Mountpoint-cache hash table entries: 2048 (order: 2, 16384 bytes, linear) [ 0.055854] cblist_init_generic: Setting adjustable number of callback queues. [ 0.063337] cblist_init_generic: Setting shift to 1 and lim to 1. [ 0.069645] cblist_init_generic: Setting adjustable number of callback queues. [ 0.077053] cblist_init_generic: Setting shift to 1 and lim to 1. [ 0.083462] rcu: Hierarchical SRCU implementation. [ 0.088379] rcu: Max phase no-delay instances is 1000. [ 0.094492] Platform MSI: msi-controller@1820000 domain created [ 0.101120] EFI services will not be available. [ 0.106102] smp: Bringing up secondary CPUs ... [ 0.111485] Detected VIPT I-cache on CPU1 [ 0.111619] GICv3: CPU1: found redistributor 1 region 0:0x00000000018a0000 [ 0.111640] GICv3: CPU1: using allocated LPI pending table @0x0000000080050000 [ 0.111704] CPU1: Booted secondary processor 0x0000000001 [0x410fd034] [ 0.111833] smp: Brought up 1 node, 2 CPUs [ 0.141285] SMP: Total of 2 processors activated. [ 0.146106] CPU features: detected: 32-bit EL0 Support [ 0.151389] CPU features: detected: CRC32 instructions [ 0.156712] CPU: All CPU(s) started at EL2 [ 0.160906] alternatives: applying system-wide alternatives [ 0.168307] devtmpfs: initialized [ 0.181641] clocksource: jiffies: mask: 0xffffffff max_cycles: 0xffffffff, max_idle_ns: 7645041785100000 ns [ 0.191693] futex hash table entries: 512 (order: 3, 32768 bytes, linear) [ 0.204585] pinctrl core: initialized pinctrl subsystem [ 0.210809] DMI not present or invalid. [ 0.215491] NET: Registered PF_NETLINK/PF_ROUTE protocol family [ 0.222786] DMA: preallocated 128 KiB GFP_KERNEL pool for atomic allocations [ 0.230142] DMA: preallocated 128 KiB GFP_KERNEL|GFP_DMA pool for atomic allocations [ 0.238159] DMA: preallocated 128 KiB GFP_KERNEL|GFP_DMA32 pool for atomic allocations [ 0.246367] audit: initializing netlink subsys (disabled) [ 0.252185] audit: type=2000 audit(0.160:1): state=initialized audit_enabled=0 res=1 [ 0.252699] thermal_sys: Registered thermal governor 'step_wise' [ 0.260145] thermal_sys: Registered thermal governor 'power_allocator' [ 0.266507] cpuidle: using governor menu [ 0.277433] hw-breakpoint: found 6 breakpoint and 4 watchpoint registers. [ 0.284450] ASID allocator initialised with 65536 entries [ 0.304592] KASLR disabled due to lack of seed [ 0.316116] HugeTLB: registered 1.00 GiB page size, pre-allocated 0 pages [ 0.323114] HugeTLB: 0 KiB vmemmap can be freed for a 1.00 GiB page [ 0.329534] HugeTLB: registered 32.0 MiB page size, pre-allocated 0 pages [ 0.336482] HugeTLB: 0 KiB vmemmap can be freed for a 32.0 MiB page [ 0.342897] HugeTLB: registered 2.00 MiB page size, pre-allocated 0 pages [ 0.349844] HugeTLB: 0 KiB vmemmap can be freed for a 2.00 MiB page [ 0.356259] HugeTLB: registered 64.0 KiB page size, pre-allocated 0 pages [ 0.363206] HugeTLB: 0 KiB vmemmap can be freed for a 64.0 KiB page [ 0.371327] k3-chipinfo 43000014.chipid: Family:AM62X rev:SR1.0 JTAGID[0x0bb7e02f] Detected [ 0.381758] iommu: Default domain type: Translated [ 0.386776] iommu: DMA domain TLB invalidation policy: strict mode [ 0.393516] SCSI subsystem initialized [ 0.397551] libata version 3.00 loaded. [ 0.397781] usbcore: registered new interface driver usbfs [ 0.403445] usbcore: registered new interface driver hub [ 0.408911] usbcore: registered new device driver usb [ 0.414650] pps_core: LinuxPPS API ver. 1 registered [ 0.419738] pps_core: Software ver. 5.3.6 - Copyright 2005-2007 Rodolfo Giometti <giometti@linux.it> [ 0.429100] PTP clock support registered [ 0.433250] EDAC MC: Ver: 3.0.0 [ 0.437598] FPGA manager framework [ 0.441206] Advanced Linux Sound Architecture Driver Initialized. [ 0.448547] clocksource: Switched to clocksource arch_sys_counter [ 0.455106] VFS: Disk quotas dquot_6.6.0 [ 0.459176] VFS: Dquot-cache hash table entries: 512 (order 0, 4096 bytes) [ 0.472453] NET: Registered PF_INET protocol family [ 0.477735] IP idents hash table entries: 16384 (order: 5, 131072 bytes, linear) [ 0.486490] tcp_listen_portaddr_hash hash table entries: 512 (order: 1, 8192 bytes, linear) [ 0.495141] Table-perturb hash table entries: 65536 (order: 6, 262144 bytes, linear) [ 0.503089] TCP established hash table entries: 8192 (order: 4, 65536 bytes, linear) [ 0.511085] TCP bind hash table entries: 8192 (order: 6, 262144 bytes, linear) [ 0.518810] TCP: Hash tables configured (established 8192 bind 8192) [ 0.525517] UDP hash table entries: 512 (order: 2, 16384 bytes, linear) [ 0.532337] UDP-Lite hash table entries: 512 (order: 2, 16384 bytes, linear) [ 0.539756] NET: Registered PF_UNIX/PF_LOCAL protocol family [ 0.546119] RPC: Registered named UNIX socket transport module. [ 0.552228] RPC: Registered udp transport module. [ 0.557045] RPC: Registered tcp transport module. [ 0.561861] RPC: Registered tcp NFSv4.1 backchannel transport module. [ 0.568463] NET: Registered PF_XDP protocol family [ 0.574236] hw perfevents: enabled with armv8_cortex_a53 PMU driver, 7 counters available [ 0.584505] Initialise system trusted keyrings [ 0.589402] workingset: timestamp_bits=46 max_order=18 bucket_order=0 [ 0.600696] squashfs: version 4.0 (2009/01/31) Phillip Lougher [ 0.607404] NFS: Registering the id_resolver key type [ 0.612653] Key type id_resolver registered [ 0.616938] Key type id_legacy registered [ 0.621103] nfs4filelayout_init: NFSv4 File Layout Driver Registering... [ 0.627968] nfs4flexfilelayout_init: NFSv4 Flexfile Layout Driver Registering... [ 0.671611] Key type asymmetric registered [ 0.675830] Asymmetric key parser 'x509' registered [ 0.680890] Block layer SCSI generic (bsg) driver version 0.4 loaded (major 245) [ 0.688702] io scheduler mq-deadline registered [ 0.693369] io scheduler kyber registered [ 0.701277] pinctrl-single 4084000.pinctrl: 34 pins, size 136 [ 0.708105] pinctrl-single f4000.pinctrl: 171 pins, size 684 [ 0.720842] Serial: 8250/16550 driver, 12 ports, IRQ sharing enabled [ 0.739461] brd: module loaded [ 0.747716] loop: module loaded [ 0.755122] tun: Universal TUN/TAP device driver, 1.6 [ 0.761232] VFIO - User Level meta-driver version: 0.3 [ 0.768073] usbcore: registered new interface driver uas [ 0.773622] usbcore: registered new interface driver usb-storage [ 0.779797] usbcore: registered new interface driver ums-sddr09 [ 0.785887] usbcore: registered new interface driver ums-sddr55 [ 0.792490] UDC core: g_mass_storage: couldn't find an available UDC [ 0.799664] i2c_dev: i2c /dev entries driver [ 0.806284] sdhci: Secure Digital Host Controller Interface driver [ 0.812685] sdhci: Copyright(c) Pierre Ossman [ 0.817369] sdhci-pltfm: SDHCI platform and OF driver helper [ 0.823779] ledtrig-cpu: registered to indicate activity on CPUs [ 0.830139] SMCCC: SOC_ID: ARCH_SOC_ID not implemented, skipping .... [ 0.837117] usbcore: registered new interface driver usbhid [ 0.842831] usbhid: USB HID core driver [ 0.847971] SPI driver ti-dac7612 has no spi_device_id for ti,dac7612 [ 0.854601] SPI driver ti-dac7612 has no spi_device_id for ti,dac7612u [ 0.861285] SPI driver ti-dac7612 has no spi_device_id for ti,dac7612ub [ 0.868127] optee: probing for conduit method. [ 0.872735] optee: revision 4.0 (2a5b1d12) [ 0.873062] optee: dynamic shared memory is enabled [ 0.882700] optee: initialized driver [ 0.888520] Initializing XFRM netlink socket [ 0.893033] NET: Registered PF_PACKET protocol family [ 0.898290] Key type dns_resolver registered [ 0.903140] registered taskstats version 1 [ 0.907379] Loading compiled-in X.509 certificates [ 0.922406] ti-sci 44043000.system-controller: ABI: 3.1 (firmware rev 0x0009 '9.1.8--v09.01.08 (Kool Koala)') [ 1.025108] lm73 2-0049: sensor 'lm73' [ 1.029779] lm73 2-004a: sensor 'lm73' [ 1.033681] omap_i2c 4900000.i2c: bus 2 rev0.12 at 100 kHz [ 1.040659] i2c 0-0030: Fixed dependency cycle(s) with /bus@f0000/i2c@20000000/pmic@30/regulators/buck2 [ 1.081284] input: tps65219-pwrbutton as /devices/platform/bus@f0000/20000000.i2c/i2c-0/0-0030/tps65219-pwrbutton.2.auto/input/input0 [ 1.093929] evbug: Connected device: input0 (tps65219-pwrbutton at tps65219-pwrbutton/input0) [ 1.095633] rtc-ds1307 0-0032: oscillator failed, set time! [ 1.101547] rtc-ds1307 0-0032: registered as rtc0 [ 1.106524] rtc-ds1307 0-0032: hctosys: unable to read the hardware clock [ 1.115517] at24 0-0050: supply vcc not found, using dummy regulator [ 1.122517] at24 0-0050: 256 byte 24c02 EEPROM, writable, 16 bytes/write [ 1.129463] omap_i2c 20000000.i2c: bus 0 rev0.12 at 400 kHz [ 1.135831] ti-sci-intr 4210000.interrupt-controller: Interrupt Router 5 domain created [ 1.144280] ti-sci-intr bus@f0000:interrupt-controller@a00000: Interrupt Router 3 domain created [ 1.153559] ti-sci-inta 48000000.interrupt-controller: Interrupt Aggregator domain 28 created [ 1.164359] ti-udma 485c0100.dma-controller: Number of rings: 82 [ 1.172797] ti-udma 485c0100.dma-controller: Channels: 48 (bchan: 18, tchan: 12, rchan: 18) [ 1.184024] ti-udma 485c0000.dma-controller: Number of rings: 150 [ 1.194426] ti-udma 485c0000.dma-controller: Channels: 35 (tchan: 20, rchan: 15) [ 1.204909] printk: console [ttyS2] disabled [ 1.209396] 2800000.serial: ttyS2 at MMIO 0x2800000 (irq = 287, base_baud = 3000000) is a 8250 [ 1.218307] printk: console [ttyS2] enabled [ 1.226773] printk: bootconsole [ns16550a0] disabled [ 1.238092] 2810000.serial: ttyS0 at MMIO 0x2810000 (irq = 288, base_baud = 3000000) is a 8250 [ 1.247827] 2820000.serial: ttyS3 at MMIO 0x2820000 (irq = 289, base_baud = 3000000) is a 8250 [ 1.257577] 2830000.serial: ttyS5 at MMIO 0x2830000 (irq = 290, base_baud = 3000000) is a 8250 [ 1.267274] 2840000.serial: ttyS6 at MMIO 0x2840000 (irq = 291, base_baud = 3000000) is a 8250 [ 1.277001] 2850000.serial: ttyS4 at MMIO 0x2850000 (irq = 292, base_baud = 3000000) is a 8250 [ 1.286684] 2860000.serial: ttyS7 at MMIO 0x2860000 (irq = 293, base_baud = 3000000) is a 8250 [ 1.303053] davinci_mdio 8000f00.mdio: Configuring MDIO in manual mode [ 1.348558] davinci_mdio 8000f00.mdio: davinci mdio revision 9.7, bus freq 1000000 [ 1.357443] am65-cpsw-nuss 8000000.ethernet: initializing am65 cpsw nuss version 0x6BA01103, cpsw version 0x6BA81103 Ports: 3 quirks:00000006 [ 1.370386] am65-cpsw-nuss 8000000.ethernet: initialized cpsw ale version 1.5 [ 1.377528] am65-cpsw-nuss 8000000.ethernet: ALE Table size 512 [ 1.384310] am65-cpsw-nuss 8000000.ethernet: CPTS ver 0x4e8a010c, freq:500000000, add_val:1 pps:0 [ 1.394826] am65-cpsw-nuss 8000000.ethernet: set new flow-id-base 19 [ 1.405858] xhci-hcd xhci-hcd.3.auto: xHCI Host Controller [ 1.411463] xhci-hcd xhci-hcd.3.auto: new USB bus registered, assigned bus number 1 [ 1.419288] xhci-hcd xhci-hcd.3.auto: USB3 root hub has no ports [ 1.425302] xhci-hcd xhci-hcd.3.auto: hcc params 0x0258fe6d hci version 0x110 quirks 0x0000008020010010 [ 1.434762] xhci-hcd xhci-hcd.3.auto: irq 300, io mem 0x31100000 [ 1.441067] usb usb1: New USB device found, idVendor=1d6b, idProduct=0002, bcdDevice= 6.01 [ 1.449343] usb usb1: New USB device strings: Mfr=3, Product=2, SerialNumber=1 [ 1.456578] usb usb1: Product: xHCI Host Controller [ 1.461461] usb usb1: Manufacturer: Linux 6.1.80-6.7.0-devel+git.603f75dc931d xhci-hcd [ 1.469382] usb usb1: SerialNumber: xhci-hcd.3.auto [ 1.474881] hub 1-0:1.0: USB hub found [ 1.478673] hub 1-0:1.0: 1 port detected [ 1.587893] cpufreq: cpufreq_online: ->get() failed [ 1.592961] cpufreq: cpufreq_online: ->get() failed [ 1.597873] cpufreq-dt cpufreq-dt: failed register driver: -19 [ 1.605791] mmc0: CQHCI version 5.10 [ 1.611151] gpio-427 (CTRL_SLEEP_MOCI#): hogged as output/high [ 1.624772] debugfs: Directory 'spi0.3' with parent 'regmap' already present! [ 1.631983] debugfs: Directory 'spi0.3' with parent 'regmap' already present! [ 1.639312] debugfs: Directory 'spi0.3' with parent 'regmap' already present! [ 1.646574] max310x spi0.3: MAX14830 ID 0xff does not match [ 1.647181] mmc0: SDHCI controller on fa10000.mmc [fa10000.mmc] using ADMA 64-bit [ 1.652802] ad7606 spi1.0: failed to RESET: no RESET GPIO specified [ 1.690483] ad7606 spi1.1: failed to RESET: no RESET GPIO specified [ 1.717790] mmc0: new HS200 MMC card at address 0001 [ 1.723739] mmcblk0: mmc0:0001 Q2J55L 7.09 GiB [ 1.724900] ad7606 spi2.0: failed to RESET: no RESET GPIO specified [ 1.734963] mmcblk0: p1 p2 [ 1.738663] mmcblk0boot0: mmc0:0001 Q2J55L 16.0 MiB [ 1.745190] mmcblk0boot1: mmc0:0001 Q2J55L 16.0 MiB [ 1.751390] mmcblk0rpmb: mmc0:0001 Q2J55L 4.00 MiB, chardev (241:0) [ 1.758624] davinci_mdio 8000f00.mdio: Configuring MDIO in manual mode [ 1.804547] davinci_mdio 8000f00.mdio: davinci mdio revision 9.7, bus freq 1000000 [ 1.818383] mdio_bus 8000f00.mdio: MDIO device at address 7 is missing. [ 1.825049] davinci_mdio 8000f00.mdio: phy[0]: device 8000f00.mdio:00, driver TI DP83867 [ 1.834887] debugfs: Directory 'pd:182' with parent 'pm_genpd' already present! [ 1.855969] ALSA device list: [ 1.859008] No soundcards found. [ 1.867911] EXT4-fs (mmcblk0p2): INFO: recovery required on readonly filesystem [ 1.875306] EXT4-fs (mmcblk0p2): write access will be enabled during recovery [ 2.766564] EXT4-fs (mmcblk0p2): recovery complete [ 2.773349] EXT4-fs (mmcblk0p2): mounted filesystem with ordered data mode. Quota mode: none. [ 2.781970] VFS: Mounted root (ext4 filesystem) readonly on device 179:2. [ 2.789505] devtmpfs: mounted [ 2.794050] Freeing unused kernel memory: 2240K [ 2.798703] Run /sbin/init as init process [ 2.802804] with arguments: [ 2.802811] /sbin/init [ 2.802816] with environment: [ 2.802821] HOME=/ [ 2.802826] TERM=linux [ 2.933389] systemd[1]: System time before build time, advancing clock. [ 2.976726] systemd[1]: systemd 250.5+ running in system mode (+PAM -AUDIT -SELINUX -APPARMOR +IMA -SMACK +SECCOMP -GCRYPT -GNUTLS -OPENSSL +ACL +BLKID -CURL -ELFUTILS -FIDO2 -IDN2 -IDN -IPTC +KMOD -LIBCRYPTSETUP +LIBFDISK -PCRE2 -PWQUALITY -P11KIT -QRENCODE -BZIP2 -LZ4 -XZ -ZLIB +ZSTD -BPF_FRAMEWORK +XKBCOMMON +UTMP +SYSVINIT default-hierarchy=hybrid) [ 3.008674] systemd[1]: Detected architecture arm64. [ 3.069446] systemd[1]: Hostname set to <verdin-am62-15415780>. [ 3.406351] systemd[1]: Binding to IPv6 address not available since kernel does not support IPv6. [ 3.415342] systemd[1]: Binding to IPv6 address not available since kernel does not support IPv6. [ 3.514479] systemd[1]: Binding to IPv6 address not available since kernel does not support IPv6. [ 3.548663] systemd[1]: Queued start job for default target Graphical Interface. [ 3.607130] systemd[1]: Created slice Slice /system/getty. [ 3.631198] systemd[1]: Created slice Slice /system/modprobe. [ 3.655190] systemd[1]: Created slice Slice /system/serial-getty. [ 3.678480] systemd[1]: Created slice User and Session Slice. [ 3.701129] systemd[1]: Started Dispatch Password Requests to Console Directory Watch. [ 3.724957] systemd[1]: Started Forward Password Requests to Wall Directory Watch. [ 3.749081] systemd[1]: Reached target Host and Network Name Lookups. [ 3.772706] systemd[1]: Reached target Path Units. [ 3.788715] systemd[1]: Reached target Remote File Systems. [ 3.808691] systemd[1]: Reached target Slice Units. [ 3.824705] systemd[1]: Reached target Swaps. [ 3.871849] systemd[1]: Listening on RPCbind Server Activation Socket. [ 3.892973] systemd[1]: Reached target RPC Port Mapper. [ 3.913656] systemd[1]: Listening on Syslog Socket. [ 3.929216] systemd[1]: Listening on initctl Compatibility Named Pipe. [ 3.953678] systemd[1]: Listening on Journal Audit Socket. [ 3.977430] systemd[1]: Listening on Journal Socket (/dev/log). [ 4.001439] systemd[1]: Listening on Journal Socket. [ 4.021738] systemd[1]: Listening on Network Service Netlink Socket. [ 4.045609] systemd[1]: Listening on udev Control Socket. [ 4.069289] systemd[1]: Listening on udev Kernel Socket. [ 4.089334] systemd[1]: Listening on User Database Manager Socket. [ 4.133371] systemd[1]: Mounting Huge Pages File System... [ 4.153992] systemd[1]: Mounting POSIX Message Queue File System... [ 4.182095] systemd[1]: Mounting Kernel Debug File System... [ 4.197374] systemd[1]: Kernel Trace File System was skipped because of a failed condition check (ConditionPathExists=/sys/kernel/tracing). [ 4.216235] systemd[1]: Mounting Temporary Directory /tmp... [ 4.243302] systemd[1]: Starting Create List of Static Device Nodes... [ 4.270760] systemd[1]: Starting Load Kernel Module configfs... [ 4.317637] systemd[1]: Starting Load Kernel Module drm... [ 4.340461] systemd[1]: Starting Load Kernel Module fuse... [ 4.361976] fuse: init (API version 7.37) [ 4.373562] systemd[1]: Starting RPC Bind... [ 4.399731] systemd[1]: Starting File System Check on Root Device... [ 4.437467] systemd[1]: Starting Journal Service... [ 4.453696] systemd[1]: Load Kernel Modules was skipped because all trigger condition checks failed. [ 4.495614] systemd[1]: Starting Generate network units from Kernel command line... [ 4.528153] systemd[1]: Starting Apply Kernel Variables... [ 4.548328] systemd[1]: Starting Coldplug All udev Devices... [ 4.592364] systemd[1]: Started RPC Bind. [ 4.614071] systemd[1]: Mounted Huge Pages File System. [ 4.645754] systemd[1]: Started Journal Service. [ 5.019170] EXT4-fs (mmcblk0p2): re-mounted. Quota mode: none. [ 5.107673] systemd-journald[156]: Received client request to flush runtime journal. [ 5.274510] audit: type=1334 audit(1651167747.340:2): prog-id=5 op=LOAD [ 5.282843] audit: type=1334 audit(1651167747.348:3): prog-id=6 op=LOAD [ 6.315835] random: crng init done [ 6.457505] pwm-backlight backlight-mezzanine: supply power not found, using dummy regulator [ 6.478837] bridge: filtering via arp/ip/ip6tables is no longer available by default. Update your scripts to load br_netfilter if you need this. [ 6.559742] ksz-switch spi0.1: found switch: LAN9374, rev 1 [ 6.622077] ksz-switch spi0.1: found switch: LAN9374, rev 1 [ 6.651482] ksz-switch spi0.1: found switch: LAN9374, rev 1 [ 6.666361] ksz-switch spi0.1: found switch: LAN9374, rev 1 [ 6.768924] ina2xx 2-0040: power monitor ina260 (Rshunt = 0 uOhm) [ 6.775416] k3-m4-rproc 5000000.m4fss: device does not reserved memory regions, ret = -22 [ 6.802850] omap8250 2b300000.serial: No clock speed specified: using default: 48000000 [ 6.819543] 2b300000.serial: ttyS1 at MMIO 0x2b300000 (irq = 491, base_baud = 3000000) is a 8250 [ 6.820889] ina2xx 2-0041: power monitor ina260 (Rshunt = 0 uOhm) [ 6.835420] k3-m4-rproc 5000000.m4fss: reserved memory init failed, ret = -22 [ 6.845856] remoteproc remoteproc0: releasing 5000000.m4fss [ 6.863211] ksz-switch spi0.1: found switch: LAN9374, rev 1 [ 6.868654] k3-m4-rproc: probe of 5000000.m4fss failed with error -22 [ 6.878852] ina2xx 2-0042: power monitor ina260 (Rshunt = 0 uOhm) [ 6.887890] ksz-switch spi0.1: found switch: LAN9374, rev 1 [ 6.898528] ina2xx 2-0043: power monitor ina260 (Rshunt = 0 uOhm) [ 6.906761] ksz-switch spi0.1: found switch: LAN9374, rev 1 [ 6.917368] ina2xx 2-0044: power monitor ina260 (Rshunt = 0 uOhm) [ 6.933419] ksz-switch spi0.1: found switch: LAN9374, rev 1 [ 6.942865] ina2xx 2-0045: power monitor ina260 (Rshunt = 0 uOhm) [ 6.965396] ksz-switch spi0.1: found switch: LAN9374, rev 1 [ 6.985245] ina2xx 2-0046: power monitor ina260 (Rshunt = 0 uOhm) [ 7.002987] ksz-switch spi0.1: found switch: LAN9374, rev 1 [ 7.026680] ina2xx 2-0047: power monitor ina260 (Rshunt = 0 uOhm) [ 7.034634] ksz-switch spi0.1: found switch: LAN9374, rev 1 [ 7.039227] ina2xx 2-004b: power monitor ina260 (Rshunt = 0 uOhm) [ 7.054557] ksz-switch spi0.1: found switch: LAN9374, rev 1 [ 7.220777] ksz-switch spi0.1: found switch: LAN9374, rev 1 [ 7.228034] rtc-ti-k3 2b1f0000.rtc: registered as rtc1 [ 7.256193] platform 78000000.r5f: R5F core may have been powered on by a different host, programmed state (0) != actual state (1) [ 7.266300] pvrsrvkm: loading out-of-tree module taints kernel. [ 7.276285] ksz-switch spi0.1: found switch: LAN9374, rev 1 [ 7.292851] platform 78000000.r5f: configured R5F for IPC-only mode [ 7.299834] platform 78000000.r5f: device does not have reserved memory regions, ret = -22 [ 7.308442] k3_r5_rproc bus@f0000:bus@b00000:r5fss@78000000: reserved memory init failed, ret = -22 [ 7.327181] ksz-switch spi0.1: found switch: LAN9374, rev 1 [ 7.345156] [drm] Initialized tidss 1.0.0 20180215 for 30200000.dss on minor 0 [ 7.367687] Console: switching to colour frame buffer device 240x67 [ 7.368657] remoteproc remoteproc0: releasing 78000000.r5f [ 7.368707] k3_r5_rproc bus@f0000:bus@b00000:r5fss@78000000: k3_r5_cluster_rproc_init failed, ret = -22 [ 7.368804] k3_r5_rproc: probe of bus@f0000:bus@b00000:r5fss@78000000 failed with error -22 [ 7.465959] tidss 30200000.dss: [drm] fb0: tidssdrmfb frame buffer device [ 7.483475] PVR_K: 182: Device: fd00000.gpu [ 7.489366] ksz-switch spi0.1: found switch: LAN9374, rev 1 [ 7.523673] PVR_K: 182: Read BVNC 33.15.11.3 from HW device registers [ 7.580794] PVR_K: 182: RGX Device registered with BVNC 33.15.11.3 [ 7.629298] [drm] Initialized pvr 23.3.6512818 20170530 for fd00000.gpu on minor 1 [ 7.679071] ksz-switch spi0.1: found switch: LAN9374, rev 1 [ 9.686532] ksz-switch spi0.1: found switch: LAN9374, rev 1 [ 9.699347] remoteproc remoteproc0: 30074000.pru is available [ 9.717138] remoteproc remoteproc1: 30078000.pru is available [ 9.726949] ksz-switch spi0.1: found switch: LAN9374, rev 1 [ 10.689753] audit: type=1334 audit(1651705158.952:4): prog-id=7 op=LOAD [ 10.697483] audit: type=1334 audit(1651705158.956:5): prog-id=8 op=LOAD [ 11.190899] audit: type=1334 audit(1651705159.452:6): prog-id=9 op=LOAD [ 11.203236] audit: type=1334 audit(1651705159.464:7): prog-id=10 op=LOAD [ 12.048274] cfg80211: Loading compiled-in X.509 certificates for regulatory database [ 12.080164] cfg80211: Loaded X.509 cert 'sforshee: 00b28ddf47aef9cea7' [ 12.088466] cfg80211: Loaded X.509 cert 'wens: 61c038651aabdcf94bd0ac7ff06c7248db18c600' [ 12.249146] am65-cpsw-nuss 8000000.ethernet eth1: configuring for fixed/rgmii-rxid link mode [ 12.266839] am65-cpsw-nuss 8000000.ethernet eth1: Link is Up - 1Gbps/Full - flow control off [ 12.305372] audit: type=1334 audit(1651705160.568:8): prog-id=11 op=LOAD [ 12.314148] am65-cpsw-nuss 8000000.ethernet eth0: PHY [8000f00.mdio:00] driver [TI DP83867] (irq=359) [ 12.323641] audit: type=1334 audit(1651705160.584:9): prog-id=12 op=LOAD [ 12.325282] am65-cpsw-nuss 8000000.ethernet eth0: configuring for phy/rgmii-rxid link mode [ 12.393024] 8021q: 802.1Q VLAN Support v1.8 [ 12.397751] 8021q: adding VLAN 0 to HW filter on device eth0 [ 12.397860] 8021q: adding VLAN 0 to HW filter on device eth1 [ 12.922597] audit: type=1334 audit(1651705161.184:10): prog-id=13 op=LOAD [ 12.939344] audit: type=1334 audit(1651705161.200:11): prog-id=14 op=LOAD [ 13.480372] audit: type=1006 audit(1651705161.740:12): pid=645 uid=0 old-auid=4294967295 auid=0 tty=(none) old-ses=4294967295 ses=1 res=1 [ 13.494401] audit: type=1300 audit(1651705161.740:12): arch=c00000b7 syscall=64 success=yes exit=1 a0=8 a1=ffffd46cda60 a2=1 a3=ffff9586b020 items=0 ppid=1 pid=645 auid=0 uid=0 gid=0 euid=0 suid=0 fsuid=0 egid=0 sgid=0 fsgid=0 tty=(none) ses=1 comm="(systemd)" exe="/lib/systemd/systemd" key=(null) [ 13.522358] systemd-journald[156]: Data hash table of /run/log/journal/65337c446fa541d1b999ebf6541a26e1/system.journal has a fill level at 75.0 (2731 of 3640 items, 2097152 file size, 767 bytes per hash table item), suggesting rotation. [ 13.544371] systemd-journald[156]: /run/log/journal/65337c446fa541d1b999ebf6541a26e1/system.journal: Journal header limits reached or header out-of-date, rotating. [ 14.449006] PVR_K: 554: RGX Firmware image 'rgx.fw.33.15.11.3' loaded [ 14.462685] PVR_K: 554: Shader binary image 'rgx.sh.33.15.11.3' loaded [ 14.982641] am65-cpsw-nuss 8000000.ethernet eth0: Link is Up - 100Mbps/Full - flow control rx/tx [ 19.813664] ksz-switch spi0.1: found switch: LAN9374, rev 1 [ 19.820018] spi spi0.1: deferred probe pending [ 43.252755] kauditd_printk_skb: 12 callbacks suppressed [ 43.252785] audit: type=1334 audit(1651705191.516:18): prog-id=12 op=UNLOAD [ 43.265173] audit: type=1334 audit(1651705191.516:19): prog-id=11 op=UNLOAD

please let me know if am missing anything