Other Parts Discussed in Thread: TDA4VH, TCAN1043-Q1

Tool/software:

J784S4XG01EVM (TDA4AP, TDA4VP, TDA4AH, TDA4VH)

Revision: PROC141E4

PMIC: TPS6594133ARWERQ1

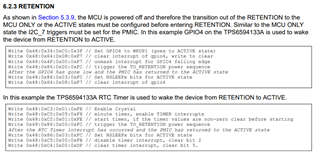

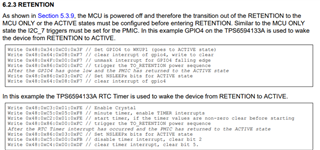

Hi Nichloas McNamara, We are currently using the J784S4XG01EVM board for our POC development work. We need your support on implementing Suspend-to-RAM functionality on the TDA4 (J784S4 EVM).