Part Number: AM6442

Tool/software:

Dear TI experts,

we are trying to integrate an update/recovery system in our Yocto distribution. For the purpose, we need to implement a functionality of a boot counter. That is:

- A counter, which is incremented on each boot trough u-boot

- The same counter is reseted, as soon as Linux has booted and certain services are online

- If the counter reaches a certain limit, the system goes into recovery mode

As you may guess, this counter has to survive resets - and optimally, but not 100% necessarily - a power cycle. So the question here: does the AM64x have such kind of non-volatile registers/memories, which survive reset, either warm or cold, or even power cycling?

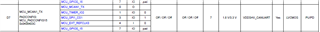

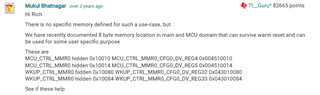

In the following forum post there is a hint, however for AM62x, so I hope that is also the case with AM64x:

Thank you!