Tool/software:

Hi Experts,

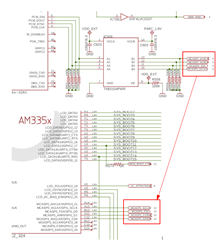

I am currently working on interfacing the AM3352 with a modem device designed to operate as a PCM Slave with a 2048 kHz clock and 8 kHz frame sync. The connection between the SoC and the modem does not involve an audio codec, and the configuration is as follows:

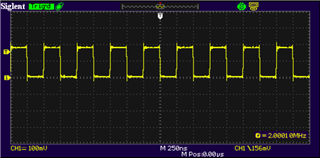

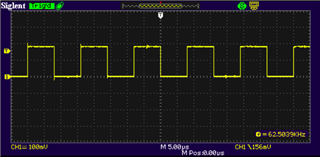

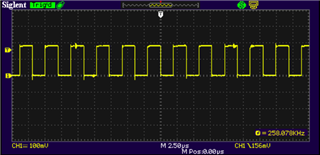

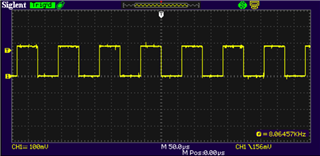

The goal is to play an audio file on the Linux side and hear the audio stream when a phone call is answered. In this case, I need the AM3352 to function as the PCM master. I have already configured the PCM interface on the AM3352, and it successfully generates a 2 MHz clock. However, with this setup, the frame sync is set to 62.5 kHz, which is not what I need.

Could you please assist me in adjusting my device tree to achieve an 8 kHz frame sync?

Below is my current device tree configuration with audio-related nodes:

sound {

compatible = "simple-audio-card";

simple-audio-card,name = "TI AM335x";

simple-audio-card,format = "i2s";

/* MCASP is master, Quectel is slave */

simple-audio-card,bitclock-master = <&cpu_dai>;

simple-audio-card,frame-master = <&cpu_dai>;

cpu_dai: simple-audio-card,cpu {

sound-dai = <&mcasp0>;

system-clock-frequency = <3072000>;

system-clock-direction-out;

};

simple-audio-card,codec {

sound-dai = <&dummy_codec>;

};

};

dummy_codec: dummy_codec {

#sound-dai-cells = <0>;

compatible = "ti,wilink8_bt";

status = "okay";

};

/* Audio interface */

mcasp0_pins: mcasp0_pins {

pinctrl-single,pins = <

AM33XX_IOPAD(0x990, PIN_OUTPUT_PULLDOWN | MUX_MODE0) /* mcasp0_aclkx - COM_AUD_CLK */

AM33XX_IOPAD(0x994, PIN_OUTPUT_PULLDOWN | MUX_MODE0) /* mcasp0_fsx - COM_AUD_FSYNC */

AM33XX_IOPAD(0x998, PIN_INPUT_PULLDOWN | MUX_MODE0) /* mcasp0_axr0 - COM_AUD_IN */

AM33XX_IOPAD(0x99c, PIN_OUTPUT_PULLDOWN | MUX_MODE2) /* mcasp0_ahclkr.mcasp0_axr2 - COM_AUD_OUT */

>;

};

/* Audio interface */

&mcasp0 {

#sound-dai-cells = <0>;

pinctrl-names = "default";

pinctrl-0 = <&mcasp0_pins>;

status = "okay";

op-mode = <0>; /* MCASP_I2S_MODE */

tdm-slots = <2>;

/* 4 serializers */

serial-dir = < /* 0: INACTIVE, 1: TX, 2: RX */

2 0 1 0 /* ARX0, ARX1, ARX2 & ARX3 */

>;

tx-num-evt = <32>;

rx-num-evt = <32>;

auxclk-fs-ratio = <256>;

};

Issue:

According to the documentation, I understand that the auxclk-fs-ratio property should be used to adjust the frame sync. However, modifying this value does not seem to change the behavior of the frame sync, which remains at 62.5 kHz.

Note: I am using ti,wilink8_bt as the dummy codec because the snd-soc-dummy driver is not functioning correctly, but I believe this is not the root cause of the issue, as it pertains to frame sync adjustment, not the codec.

I would greatly appreciate your assistance in helping me adjust the device tree so that the frame sync is set to 8 kHz as required.

Thank you for your support.