Tool/software:

Dear expert:

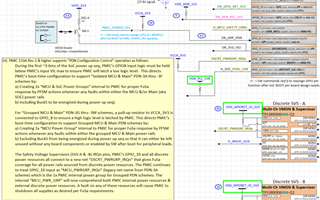

accroding to Alert J784S4 E5 J742S2 E2 EVM Sys Updates v1.0.pdf

GPIO 8 is EN_GRP_PDN type, it will latch before 3ms step of power up seruence.

I want to know the 3ms from what time to what time ?

When i connect it to Vsys_mcuio_3v3 , it seems latch 0 (I test the buck 5's output)

when i connect it to vsys_io_3v3 , it seems latch 1 I test the buck 5's output);

I am confused with the result;