Part Number: TDA4VM

Other Parts Discussed in Thread: TDA4VH

Tool/software:

Dear expert,

I'm trying to collect BIST write latency on ECC protected DRAM area, compared with CPU write in R5 u-boot.

- Ref board: J721E/TDA4 ref board

- SDK: ti-processor-sdk-linux-adas-j721e-evm-10_01_00_04

In 1st test, I write "k3_ddrss_preload_ecc_mem_region()" function in R5 u-boot,

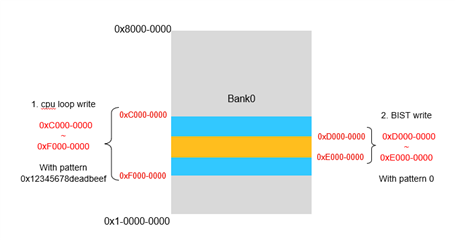

CPU loop write on 0xC000-0000 ~ 0xD000-0000 with u64 patten 0x1234-5678-dead-beef

I check the DRAM content in u-boot prompt, it works well .

| => md.l 0xc0000000 0x10 c0000000: deadbeef 12345678 deadbeef 12345678 ....xV4.....xV4. c0000010: deadbeef 12345678 deadbeef 12345678 ....xV4.....xV4. c0000020: deadbeef 12345678 deadbeef 12345678 ....xV4.....xV4. c0000030: deadbeef 12345678 deadbeef 12345678 ....xV4.....xV4. => md.l 0xcfffffe0 0x10 cfffffe0: deadbeef 12345678 deadbeef 12345678 ....xV4.....xV4. cffffff0: deadbeef 12345678 deadbeef 12345678 ....xV4.....xV4. d0000000: 008a81c1 c00090f4 1c100002 01809008 ................ d0000010: 82884431 cca20202 801010a8 65924309 1D...........C.e => |

In 2nd test, after cpu write on 0xC000-0000 ~ 0xD000-0000 with pattern 0x1234-5678-dead-beef in R5 u-boot

then I call u-boot function "k3_lpddr4_bist_init_mem_region(ddrss, 0x50000000, 0x10000000, 0x11223344)"

to initial write 0xD000-0000 ~ 0xE000-0000 with u32 pattern 0x1122-3344

But get below result in u-boot prompt

| => md.l 0xc0000000 0x10 c0000000: deadbeef 12345678 deadbeef 12345678 ....xV4.....xV4. c0000010: deadbeef 12345678 deadbeef 12345678 ....xV4.....xV4. c0000020: deadbeef 12345678 deadbeef 12345678 ....xV4.....xV4. c0000030: deadbeef 12345678 deadbeef 12345678 ....xV4.....xV4. => md.l 0xc71c71e0 0x10 c71c71e0: deadbeef 12345678 deadbeef 12345678 ....xV4.....xV4. c71c71f0: deadbeef 12345678 deadbeef 12345678 ....xV4.....xV4. c71c7200: 11223344 11223344 00000000 00000000 D3".D3"......... c71c7210: 11223344 11223344 00000000 00000000 D3".D3"......... => md.l 0xd5555560 d5555560: 11223344 11223344 00000000 00000000 D3".D3"......... d5555570: 11223344 11223344 00000000 00000000 D3".D3"......... d5555580: c8108008 14042783 091d0400 141289c4 .....'.......... d5555590: 0b894888 411488ac 410a9198 8201d814 .H.....A...A.... => |

Seems that BIST write gets 2 issues:

- DRAM range c71c7200 ~ d5555580 is not expected.

- some area is not initialized with zeros instead of pattern.

Below is my u-boot code in 2nd test, could you help check what's wrong?

| file: ti-processor-sdk-linux-adas-j721e-evm-10_01_00_04/board-support/ti-u-boot-2024.04+git/drivers/ram/k3-ddrss/k3-ddrss.c |

| static void k3_ddrss_preload_ecc_mem_region(u64 *addr, u64 size, u64 pattern) { u64 i = 0; for (i = 0; i < (size / 8); i++) addr[i] = pattern; } |

|

static void k3_ddrss_lpddr4_ecc_init(struct k3_ddrss_desc *ddrss) //... skip done = get_timer(0); done = get_timer(0); // BIST require bus addr ? am I right? (0xD000-0000 - 0x8000-0000) = 0x5000-0000 // ... skip } |

Thanks a lot for your support !

Best,

Leon