Part Number: PROCESSOR-SDK-AM335X

Tool/software:

Hello, I currently have a BeagleBone Black running a prebuilt image, ‘Debian 11.x (Bullseye) Minimal Snapshot,’ where I have already completed all the necessary configurations to run a Python Qt application at startup.

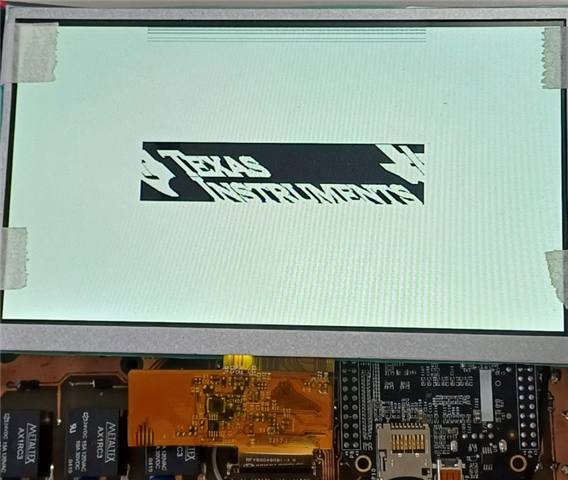

Now, I have a new requirement: adding a splash image to U-Boot.

I am following the ‘09_03_05_02’ guide from the Linux SDK, where this feature was recently added, but I am still not completely clear on the exact steps.

My idea is to use the SDK to compile a new U-Boot on my host PC, first configuring it according to section ‘3.1.2.5. U-Boot Splash Screen.’

After compiling, I would like to mount the prebuilt image I already have working on my host PC and replace the original U-Boot with the newly compiled one.

I’m not sure if this is the correct procedure. If anyone could guide me, I would greatly appreciate it.