Tool/software:

Hi experts,

SDK10, U-Boot 2024.04.

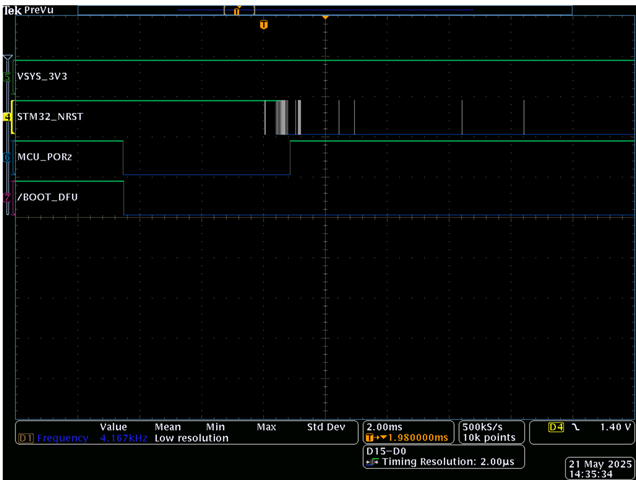

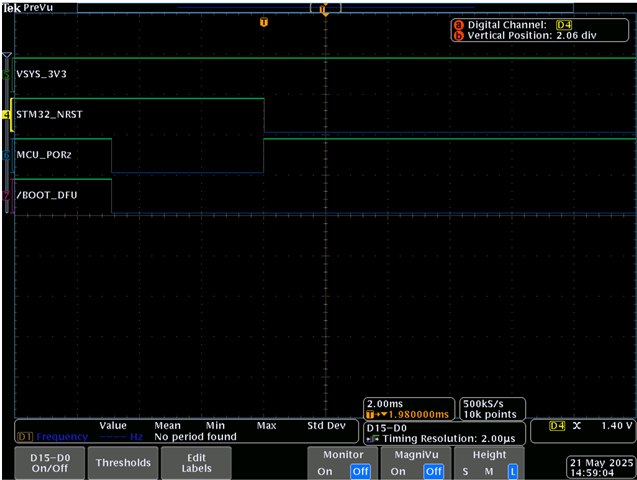

We have a custom board with an external STM32 processor acting as a reset cpu. This external cpu

is responsible for resetting the SoC or setting the boot strapping to USB (DFU) mode. The STM32

sets the corresponding boot strap and then toggles the MCU_PORz (driving it low, then high).

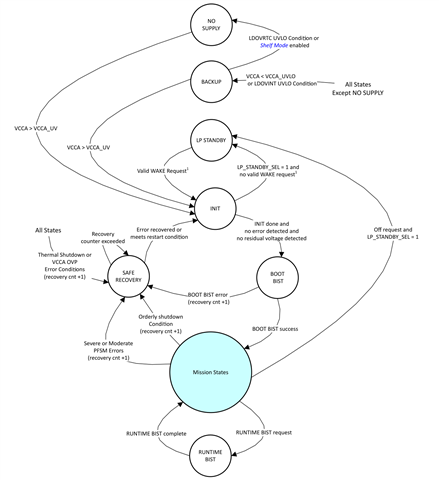

Occasionally, our board won't come alive at all. We have found that one SoC GPIO line that controls the

STM32_NRST pin is being actively driven LOW at these occasions. We have even tried setting a

really strong pull-up on that pin but the SoC still drives it low.

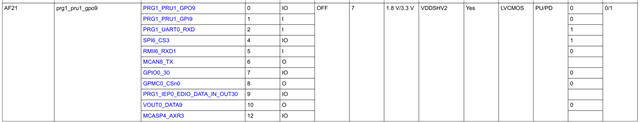

Looking at the datasheet, that pin (AF21) should have state OFF (high-impedance) at reset.

How come we see that this line is being actively driven low at reset. I can't get the board working unless I

toggle the power, which in turn releases the pin.

Is there anything that can be done to assure that this pin is "released" at reset?

Best regards,

/Bo