Tool/software:

Greetings TI Support Team,

I am looking for information related to the DMA capabilities on the AM62x processor.

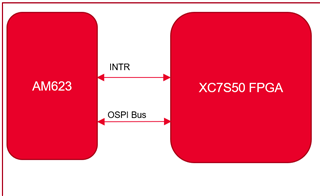

In our application, we are connecting AM623 OSPI to an external FPGA. The plan is to retrieve a block of multiple 64bit data from FPGA upon receiving an interrupt from FPGA. We would like to how to trigger DMA transfer upon receiving an interrupt from FPGA.

The following are the questions that we have currently.

- Is there an interrupt-driven DMA interface available for AM62x?

- Can this interface be used to efficiently write data to or read data from memory or peripherals?

- Are there any recommended drivers or examples available in the SDK for implementing such transfers?

Any documentation or guidance you could provide would be helpful.