Other Parts Discussed in Thread: AM62P, OMAP-L138, AM6442, DP83825I, AM623, DP83TC817S-Q1, DP83TC812S-Q1, DP83TG721S-Q1, AM263P4

Tool/software:

Hi TI experts,

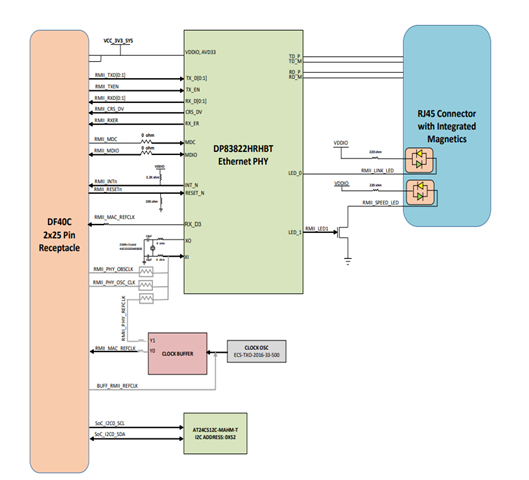

Please provide guidelines for using RMII interface

Recommendations while using TI EPHY for RMII interface