Tool/software:

Hi,

Would it be acceptable to use x16 width device for the DDR but with an x8 device ECC?

Or do they all need to be the same device / same width?

Thank you.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hi,

Would it be acceptable to use x16 width device for the DDR but with an x8 device ECC?

Or do they all need to be the same device / same width?

Thank you.

Greetings,

Please refer to the DDR layout and design guidelines. They must all be the same device and the guidelines show how it should be connected.

https://www.ti.com/lit/pdf/spraci2

Sincerely,

Lucas

Hi Lucas,

I was looking at the guidelines and had a follow-up question.

For the unused bit (DQ7) in the ECC, is it preferable to pull it up or down?

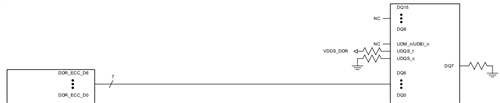

The design guidelines show DQ7 being pulled low on a x16 device in Figure 1:

However, this is not shown at all in Figure 2 for a x8 device:

(I believe this is a typo, as it maps DDR_ECC_D[6:0] to the ECC's DQ[7:0])

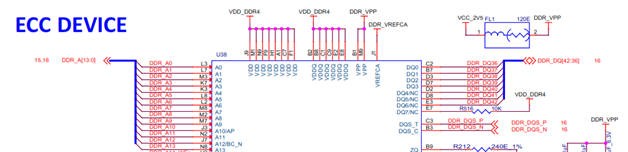

Further, the schematics for the AM65 EVM (which uses x8) shows the DQ7 being pulled high.

Is there a reason why the ECC's DQ7 is pulled low in x16 but high in x8? Please advise.

Thank you!

Greetings Michael,

The unused pins on the DRAM itself may have requirements/recommendations from the memory vendor for what to do with unused pins, but I do not believe they should not have an effect on the ECC functionality. If there are none it may also have been done to simplify the board layout, I will ask the team about this. Please note that we have our usual experts out on timebank for an extended period of time and will have a delayed response to this specific question.

Unused pins on the SoC have their guidelines in this document for what to do with them depending on DDR4/DDR3/LPDDR4.

Sincerely,

Lucas