Tool/software:

Hi, TI Team:

During the high-temperature operation test of our parking machine product, an error occurred when running the EMMC HS400.

1、Product configuration:SOC: TDA4VL21J5AALZRQ1

EMMC: Longsys FEMDME008G-A8A93

2、Test conditions and problem reproduction methods:

We placed the product in an environment temperature chamber set at 85 degrees, and powered it on for continuous operation for 30 to 60 minutes. At this point, the surface temperature of the chip reached around 98 degrees Celsius. Problems occurred under the eMMC communication HS400 rate. The probability of this issue recurring is 100%.

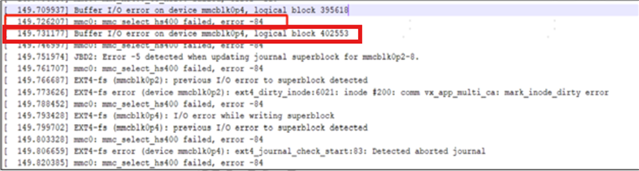

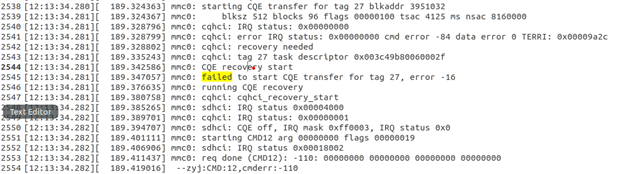

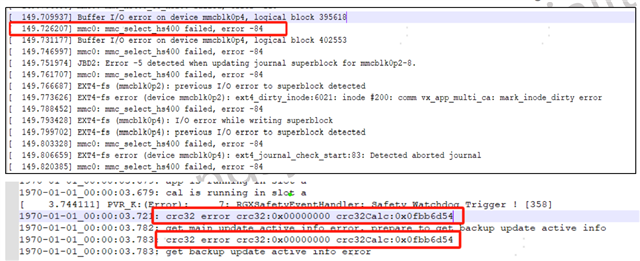

When an abnormal situation occurs, the SOC log is as follows:

In addition,Under the same testing conditions, we used Samsung's eMMC part KLM8G1GEUF-B04Q and there were no issues.

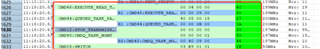

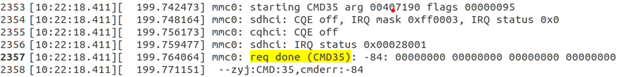

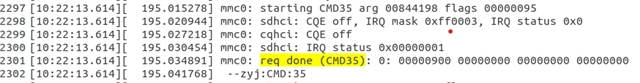

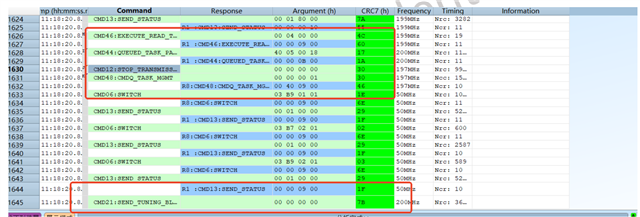

3、The eMMC manufacturer Longsys used a logic analyzer to capture the CMD and Data0 when the problem occurred.

4、The test report for EMMC data reading signals is attached. It includes data from Longsys FEMDME008G-A8A93 and Samsung KLM8G1GEUF-B04Q.

The eMMC manufacture Longsys have two question need to be answered by the TI team:

Q1: Regarding the SOC read DS Delay Tuning, is it performed only during power-on startup or does it adjust in real time based on changes such as temperature and voltage?

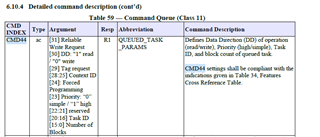

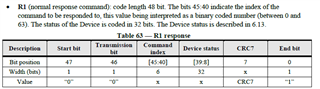

Q2: Does the EMMC PHY of the SOC have the digital eye diagram function? During the tuning process, the offset of the Ds Delay is carried out step by step, resulting in a set of De Delay values that are available within the UI time frame. This forms a digital eye diagram.

Any ideas about how to solve this issue?