Other Parts Discussed in Thread: TDA4VH

Tool/software:

Hi TI expert,

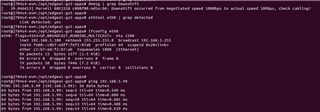

We using tda4vh custom board and using the internal switch cpsw9g with marvell PHY 88xx,

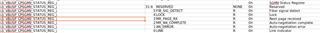

=> custom device tree with our PHY and eth0 link up, but we cannot ping in LAN connection

&serdes_ln_ctrl {

idle-states = <J784S4_SERDES1_LANE2_QSGMII_LANE1>, <J784S4_SERDES2_LANE3_QSGMII_LANE2>,

<J784S4_SERDES2_LANE0_QSGMII_LANE5>, <J784S4_SERDES2_LANE1_QSGMII_LANE6>,

<J784S4_SERDES2_LANE2_QSGMII_LANE7>, <J784S4_SERDES2_LANE3_QSGMII_LANE8>;

};

&serdes_wiz2 {

status = "okay";

};

&serdes2 {

status = "okay";

#address-cells = <1>;

#size-cells = <0>;

serdes2_qsgmii_link: phy@0 {

reg = <2>;

cdns,num-lanes = <1>;

#phy-cells = <0>;

cdns,phy-type = <PHY_TYPE_QSGMII>;

resets = <&serdes_wiz2 3>;

};

};

&main_gpio0 {

status = "okay";

};

&main_cpsw0 {

status = "okay";

};

&main_cpsw0_port5 {

status = "okay";

phy-handle = <&cpsw9g_phy2>;

phy-mode = "sgmii";

mac-address = [c2 b7 ed f2 87 ab];

phys = <&cpsw0_phy_gmii_sel 5>, <&serdes2_qsgmii_link>;

phy-names = "mac", "serdes";

reset-post-delay-us = <120000>;

};

&main_cpsw0_mdio {

status = "okay";

pinctrl-names = "default";

pinctrl-0 = <&mdio0_pins_default>;

bus_freq = <1000000>;

reset-gpios = <&main_gpio0 17 GPIO_ACTIVE_LOW>;

#address-cells = <1>;

#size-cells = <0>;

cpsw9g_phy2: ethernet-phy@6 {

reg = <6>;

};

};

&serdes_refclk {

clock-frequency = <100000000>;

};