Other Parts Discussed in Thread: SYSCONFIG,

Tool/software:

Hi,

I'm working on an AM64x-based system and would like to latch the position counter (QPOSCNT) of two eQEP modules simultaneously using a periodic signal generated by ePWM.

Here's what I'm trying to achieve:

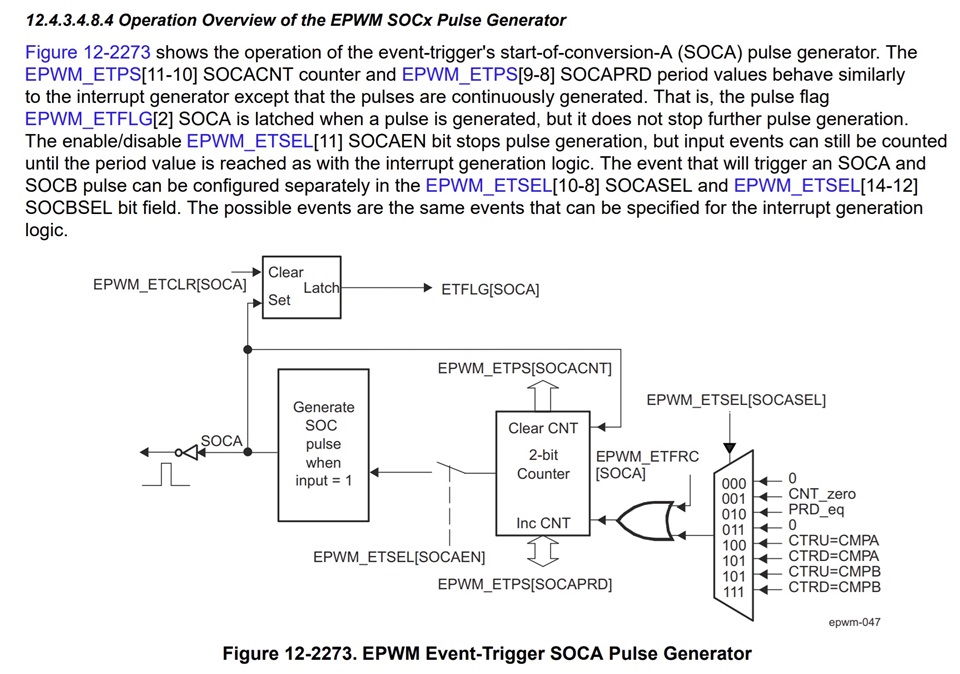

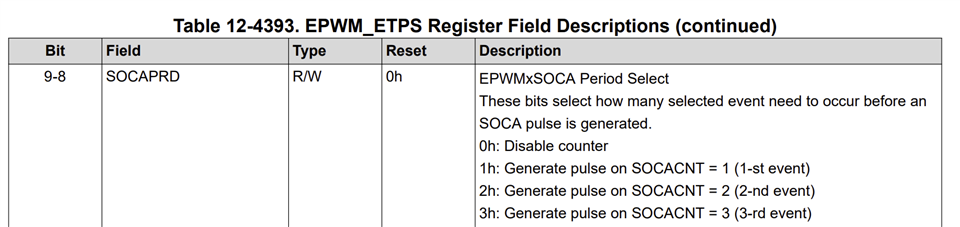

- Generate a 10Hz pulse using ePWM.

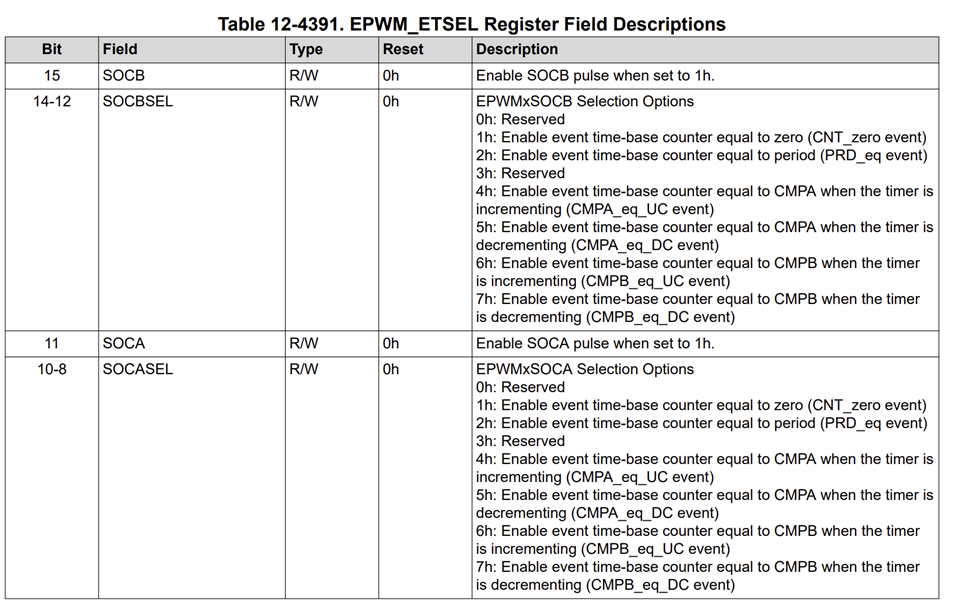

- Use ADCSOCA from ePWM as an internal trigger.

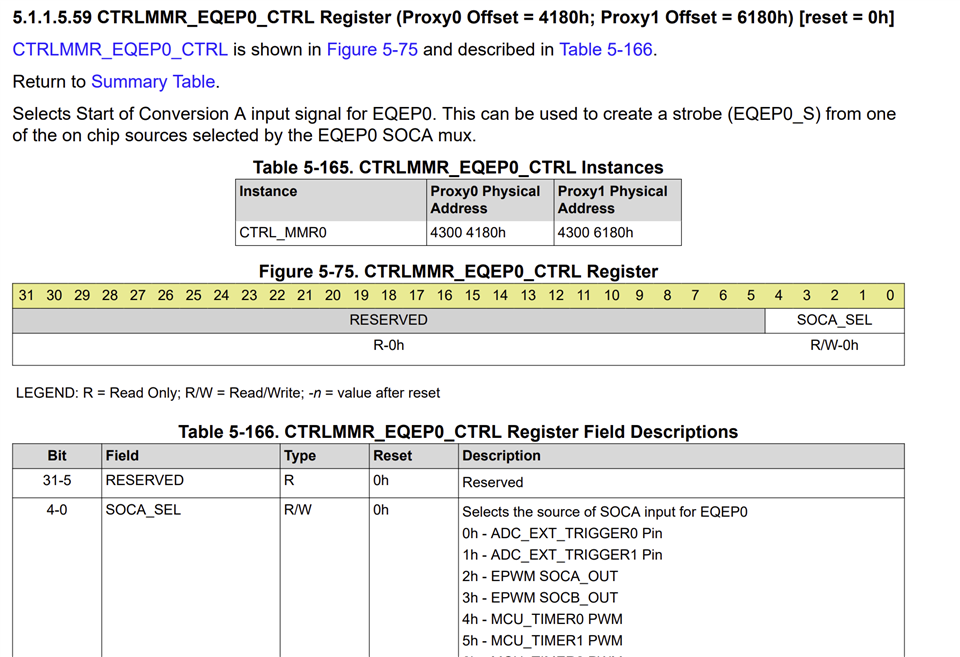

- Route this ADCSOCA signal to both eQEP0 and eQEP2 as their STROBE input.

- Configure both eQEPs to latch QPOSCNT on the rising edge of the STROBE signal.

I believe the following API calls are relevant:

EQEP_setStrobeSource(baseAddr, EQEP_STROBE_OR_ADCSOCA);

EQEP_setLatchMode(baseAddr, EQEP_LATCH_STROBE_RISING);

My questions:

- Is it valid to use the same ePWM ADCSOCA signal as the STROBE source for multiple eQEP modules?

- Are there any limitations or considerations when doing this on AM64x?

- Could you provide guidance or an example on how to configure this using SysConfig?

- Do I need to configure any crossbar or internal routing explicitly, or is this handled automatically?

Any help or example projects would be greatly appreciated!

Thanks in advance.