Tool/software:

Dear Ti,

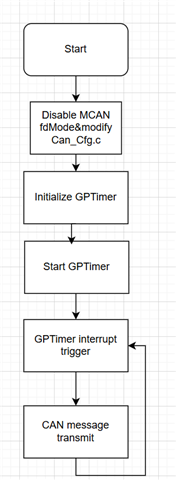

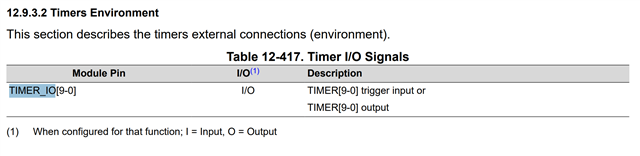

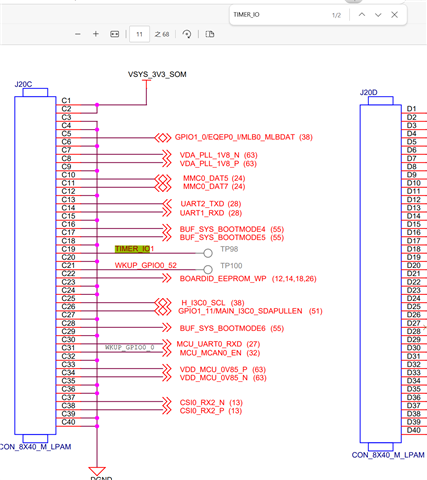

I am using Gptimer to control CAN transmission. I just want to send messages (Classical CAN) every 20 ms infinitely, so I copy sample code of Gpt directory to initialize. The patch is the files I have modified.

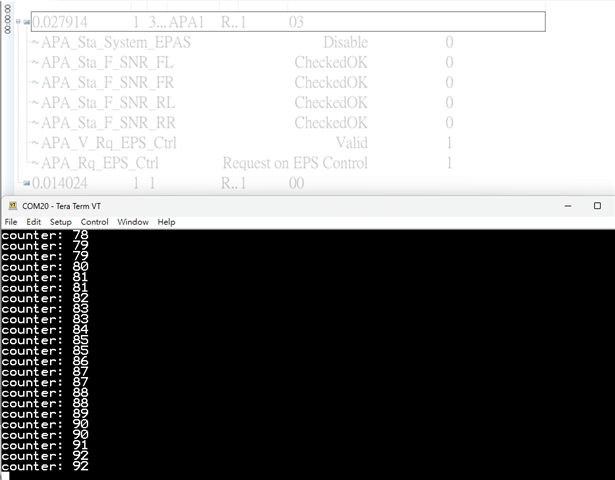

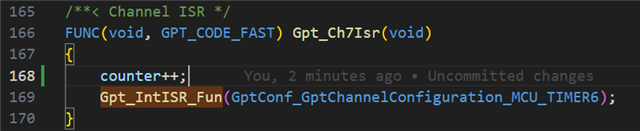

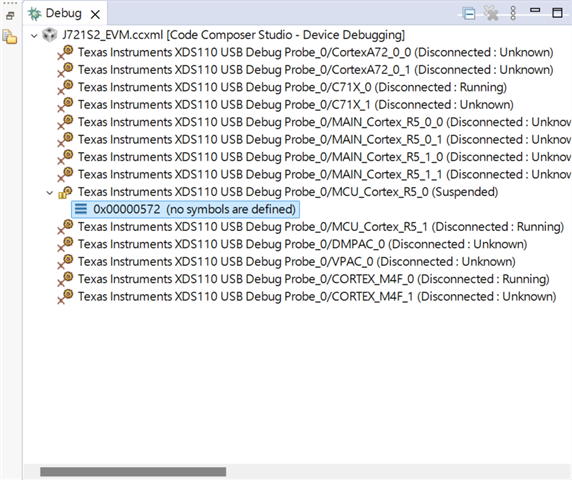

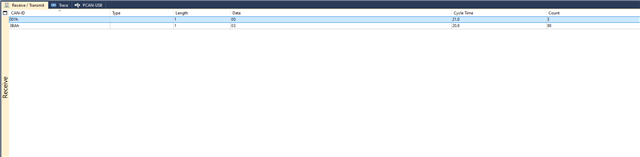

However, I don't know why the transmission always stopped after send 89 times and then it will send 3 times of 001 ID trace (CAN sent messages), after that the process just like stopped. When I click stop on ccs, it only showed like the screenshot, I don't know what it means, how can I know where in the code the program is running?

ps. all modified under directory of "ti_J721S\ti-processor-sdk-rtos-j721s2-evm-10_01_00_04", CAN_LOOPBACK_ENABLE in Can_Cfg.h set to STD_OFF

patch:

diff --git a/mcusw/build/Rules.make b/mcusw/build/Rules.make

index 5714bd26..eb70dd1d 100644

--- a/mcusw/build/Rules.make

+++ b/mcusw/build/Rules.make

@@ -130,7 +130,7 @@ endif

export device_family

# Default Build Profile

# Supported Values: debug | release

-export BUILD_PROFILE ?= release

+export BUILD_PROFILE ?= debug

# Default Build Variant

# Supported Values: precompile | linktime | postbuild

diff --git a/mcusw/mcal_drv/mcal/Can/src/Can.c b/mcusw/mcal_drv/mcal/Can/src/Can.c

index 662163a2..b512d08e 100755

--- a/mcusw/mcal_drv/mcal/Can/src/Can.c

+++ b/mcusw/mcal_drv/mcal/Can/src/Can.c

@@ -427,6 +427,10 @@ FUNC(Std_ReturnType, CAN_CODE) Can_Write(

Can_DriverObj.canController[MsgCntrlr].canTxStatus[msgObjIndx]

= 1U;

}

+ else

+ {

+ status = E_NOT_OK;

+ }

}

/* CAN_CoverageGap_31: Dynamic coverage for the below 'else' statement is not

* covered.The 'else' statement is added as an additional safety

diff --git a/mcusw/mcal_drv/mcal/Can/src/Can_Mcan.c b/mcusw/mcal_drv/mcal/Can/src/Can_Mcan.c

index d4f48472..cedb1f00 100644

--- a/mcusw/mcal_drv/mcal/Can/src/Can_Mcan.c

+++ b/mcusw/mcal_drv/mcal/Can/src/Can_Mcan.c

@@ -1806,7 +1806,7 @@ static void Can_mcanInit(MCAN_InitParams *initParams,

baseAddr = canControllerCfg_PC->CntrAddr;

/* Initialize MCAN Init params */

- initParams->fdMode = (uint32)MCAN_CCCR_FDOE_ENABLE;

+ initParams->fdMode = (uint32)MCAN_CCCR_FDOE_DISABLE;

if((boolean)TRUE ==

canControllerCfg->DefaultBaud->BaudFdRateConfig.BrsSwitch)

{

diff --git a/mcusw/mcal_drv/mcal/examples/Can/CanApp.c b/mcusw/mcal_drv/mcal/examples/Can/CanApp.c

index f23bfc42..d93028d0 100644

--- a/mcusw/mcal_drv/mcal/examples/Can/CanApp.c

+++ b/mcusw/mcal_drv/mcal/examples/Can/CanApp.c

@@ -83,14 +83,21 @@ static void CanApp_LoopbackTest(void);

#if (STD_ON == CAN_SAFETY_DIAGNOSTIC)

static void CanApp_SafetyApiTest(void);

#endif

+static void AppUtils_delay(uint32 count);

/* ========================================================================== */

/* Global Variables */

/* ========================================================================== */

uint32 CanApp_TestPassed = E_OK;

+uint8 hth = 0U;

+Std_ReturnType status = E_OK;

+uint32 GptApp_DemoStatus = E_OK;

+

/**< Variable used for Demo status */

Can_PduType CanApp_Pdu, CanApp_Pdu1;

Can_PduType CanApp_Pdu2, CanApp_Pdu3, CanApp_Pdu4, CanApp_Pdu5;

+volatile uint32 GptApp_NotifiedForInstFlag = 0xFFFF;

+extern volatile uint8 GptApp_WakeupSrcDetFlag;

/**< Variables which contains Can PDU data used in Can transmission */

uint8 CanApp_InputData[64U] =

@@ -102,6 +109,45 @@ uint8 CanApp_InputData[64U] =

0xA6, 0x6A, 0xFF, 0xFF, 0xC6, 0x6C, 0xB6, 0x6B,

0xA7, 0x7A, 0xFF, 0xFF, 0xC7, 0x7C, 0xB7, 0x7B,

0xA8, 0x8A, 0xFF, 0xFF, 0xC8, 0x8C, 0xB8, 0x8B};

+

+uint8 txData[8U];

+

+uint8 BCAN_TX_0x3BA_APA1_GetRC(void) {

+ static uint8 cnt = 0;

+ return (cnt++) & 0x0F;

+}

+

+uint8 BCAN_TX_0x3BA_APA1_GetCS(uint8 *data, uint8 roll_count) {

+ uint8 checksum = 0;

+ for (int i = 0; i < 8; i++) {

+ checksum += data[i];

+ }

+ return checksum & 0x0F;

+}

+

+void BCAN_TX_0x3BA_APA1(uint8 *data) {

+ TU_APA1_MSG *obj = (TU_APA1_MSG *)data;

+

+ obj->Bits.APA_V_Rq_EPS_Ctrl = bcanData.TX.Angle.Valid;

+ obj->Bits.APA_Rq_EPS_Ctrl = bcanData.TX.Angle.Apply;

+ obj->Bits.APA_Angle_Target_0 = (uint8)(bcanData.TX.Angle.Value >> 8);

+ obj->Bits.APA_Angle_Target_1 = (uint8)(bcanData.TX.Angle.Value & 0xFF);

+ obj->Bits.APA_Roll_Count = BCAN_TX_0x3BA_APA1_GetRC();

+ obj->Bits.APA_checksum = BCAN_TX_0x3BA_APA1_GetCS(data, obj->Bits.APA_Roll_Count);

+}

+

+#if defined (SOC_J721E) || (SOC_J7200) || defined (SOC_J721S2) || defined (SOC_J784S4) || defined (SOC_J742S2)

+FUNC(void, GPT_CODE_FAST) GptApp_GptXIsr(uintptr_t GptPtr)

+{

+ GptApp_IsrType gptChIsr = (GptApp_IsrType)GptPtr;

+

+ /* Associated GPT ISR */

+ gptChIsr();

+}

+#endif

+const Gpt_ConfigType *pCfgPtr = &GptChannelConfigSet;

+extern const struct Gpt_ChannelConfigType_PC_s Gpt_ChannelConfig_PC[GPT_MAX_CHANNELS];

+

/**< Variable which contains Can SDU data that is transported inside the PDU */

const Can_PduType *PduInfo;

/**< Variable which contains Can PDU data passed during Transmission */

@@ -120,6 +166,7 @@ extern volatile P2CONST(PduInfoType, CANIF_VAR_CLEARED, CANIF_APPL_DATA)

/* ========================================================================== */

sint32 main(void)

{

+ Gpt_Init(pCfgPtr);

CanApp_TestPassed = E_OK;

#if defined (SOC_AM62X) || defined (SOC_AM62AX) || defined (SOC_AM62DX) || defined (SOC_AM62PX) || defined (SOC_J722S)

@@ -143,9 +190,9 @@ sint32 main(void)

CanApp_PlatformInit();

CanApp_LoopbackTest();

-#if (STD_ON == CAN_SAFETY_DIAGNOSTIC)

- CanApp_SafetyApiTest();

-#endif

+// #if (STD_ON == CAN_SAFETY_DIAGNOSTIC)

+// CanApp_SafetyApiTest();

+// #endif

AppUtils_Printf(MSG_NORMAL,

"CAN Stack Usage: %d bytes\n", AppUtils_GetStackUsage());

@@ -170,175 +217,121 @@ sint32 main(void)

return (CanApp_TestPassed);

}

-static void CanApp_LoopbackTest(void)

+void AppUtils_delay (uint32 count)

{

- uint32 ctlr_cnt, mask = 0x00000000U, canMaxControllerCnt;

- uint8 loopCnt = 0U, hth = 0U;

- Std_ReturnType status;

- const Can_ConfigType *Can_ConfigPtr;

-

-#if (STD_ON == CAN_VARIANT_PRE_COMPILE)

- Can_ConfigPtr = &CAN_INIT_CONFIG_PC;

-#else

- Can_ConfigPtr = &CanConfigSet;

-#endif

+ volatile uint32 x = count;

+ while (x)

+ x--;

+}

- canMaxControllerCnt = Can_ConfigPtr->CanMaxControllerCount;

- for (ctlr_cnt = 0U; ctlr_cnt < canMaxControllerCnt;

- ctlr_cnt++)

+void Gpt_Channel_Notify12(void)

+{

+ // AppUtils_Printf(MSG_NORMAL, "Can_Gpt: GPT Notification received for channel 11 !!!\n");

+ status = Can_Write(hth, PduInfo);

+ if (status != E_OK)

{

- /* Set Can frame */

- CanApp_SetupCanFrame(ctlr_cnt, &hth, &mask);

-

- /* Set Controller Mode to Start */

- status = Can_SetControllerMode(

- CanConfigSet_CanController_List_PC[ctlr_cnt]->ControllerId, CAN_CS_STARTED);

- if (status != E_OK)

- {

- CanApp_TestPassed = E_NOT_OK;

- }

-

-#if (CAN_LOOPBACK_ENABLE == STD_ON)

- /* Enable loopback mode in CAN */

- Can_TestLoopBackModeEnable(

- CanConfigSet_CanController_List_PC[ctlr_cnt]->ControllerId, 0U);

-#endif

-

- /* Do Can Write to send the CanApp_InputData on CAN bus */

- status = Can_Write(hth, PduInfo);

-

-#if defined (SOC_AM62X) || defined (SOC_AM62AX) || defined (SOC_AM62DX) || defined (SOC_AM62PX) || defined (SOC_J722S)

- Can_MainFunction_Write();

- for(int cnt=0; cnt<100000;cnt++)

- {

- ;

- }

-#endif

+ AppUtils_Printf(MSG_NORMAL,

+ "CAN_APP: Error In Can_Write.\n");

+ CanApp_TestPassed = E_NOT_OK;

+ }

+ else

+ {

+ BCAN_TX_0x3BA_APA1(txData);

+ }

+ GptApp_NotifiedForInstFlag = 11U; /* Set it to channel number */

+}

- if (status != E_OK)

- {

- AppUtils_Printf(MSG_NORMAL,

- "CAN_APP: Error In Can_Write.\n");

- CanApp_TestPassed = E_NOT_OK;

- }

+void Gpt_Channel_Notify7(void)

+{

+ // AppUtils_Printf(MSG_NORMAL, "Can_Gpt: GPT Notification received for channel 6 !!!\n");

+ status = Can_Write(hth, PduInfo);

+ if (status != E_OK)

+ {

+ AppUtils_Printf(MSG_NORMAL,

+ "CAN_APP: Error In Can_Write.\n");

+ CanApp_TestPassed = E_NOT_OK;

+ }

+ else

+ {

+ BCAN_TX_0x3BA_APA1(txData);

+ }

+ GptApp_NotifiedForInstFlag = 6U; /* Set it to channel number */

+}

- while ((CanIf_TxConfirmationCount != 1U))

- {

- /* Wait for Tx Confirmation */

-#if defined (SOC_AM62X) || defined (SOC_AM62AX) || defined (SOC_AM62DX) || defined (SOC_AM62PX) || defined (SOC_J722S)

- Can_MainFunction_Write();

- for(int cnt=0; cnt<10000;cnt++)

- {

- ;

- }

-#endif

+void Gpt_Channel_Notify10(void)

+{

+ AppUtils_Printf(MSG_NORMAL, "Can_Gpt: GPT Notification received for channel 9 !!!\n");

+ GptApp_NotifiedForInstFlag = 9U; /* Set it to channel number */

+}

- }

+void Gpt_Channel_Notify16(void)

+{

+ AppUtils_Printf(MSG_NORMAL, "Can_Gpt: GPT Notification received for channel 15 !!!\n");

+ GptApp_NotifiedForInstFlag = 15U; /* Set it to channel number */

+}

-#if defined (SOC_AM62X) || defined (SOC_AM62AX) || defined (SOC_AM62DX) || defined (SOC_AM62PX) || defined (SOC_J722S)

- Can_MainFunction_Read();

+#if defined (SOC_J7200) || defined (SOC_J721S2) || defined (SOC_J784S4) || defined (SOC_J742S2)

+void Gpt_Channel_Notify18(void)

+{

+ AppUtils_Printf(MSG_NORMAL, "Can_Gpt: GPT Notification received for channel 18 !!!\n");

+ GptApp_NotifiedForInstFlag = 17U; /* Set it to channel number */

+}

#endif

- if (E_OK == CanApp_TestPassed)

- {

- if ((1U == CanIf_TxConfirmationCount) &&

- (1U == CanIf_RxConfirmationCount))

- {

- CanIf_TxConfirmationCount = 0U;

- CanIf_RxConfirmationCount = 0U;

- }

- else

- {

- CanApp_TestPassed = E_NOT_OK;

- break;

- }

-

- /* Set Controller Mode to Stop*/

- status = Can_SetControllerMode(

- CanConfigSet_CanController_List_PC[ctlr_cnt]->ControllerId,

- CAN_CS_STOPPED);

- if (status != E_OK)

- {

- CanApp_TestPassed = E_NOT_OK;

- }

+static void CanApp_LoopbackTest(void)

+{

+ uint32 mask = 0x00000000U, countVal;

+ Gpt_ChannelType chId;

+

+ bcanData.TX.Angle.Valid = 1;

+ bcanData.TX.Angle.Apply = 1;

+ bcanData.TX.Angle.Value = 0x2328;

+

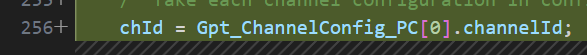

+ /* Take each channel configuration in configuration set */

+ chId = Gpt_ChannelConfig_PC[1].channelId;

+ /* Set Can frame */

+ CanApp_SetupCanFrame(0, &hth, &mask);

+

+ /* Set Controller Mode to Start */

+ status = Can_SetControllerMode(

+ CanConfigSet_CanController_List_PC[0]->ControllerId, CAN_CS_STARTED);

+ if (status != E_OK)

+ {

+ CanApp_TestPassed = E_NOT_OK;

+ }

#if (CAN_LOOPBACK_ENABLE == STD_ON)

- Can_TestLoopBackModeDisable(

- CanConfigSet_CanController_List_PC[ctlr_cnt]->ControllerId, 0U);

+ /* Enable loopback mode in CAN */

+ Can_TestLoopBackModeEnable(

+ CanConfigSet_CanController_List_PC[0]->ControllerId, 0U);

#endif

- if ((PduInfo->length == CanIf_PduInfoPtr->SduLength) &&

- (PduInfo->id == (CanIf_Mailbox->CanId | mask)))

- {

-#if defined (SOC_AM62X) || defined (SOC_AM62AX) || defined (SOC_AM62DX) || defined (SOC_AM62PX) || defined (SOC_J722S)

- AppUtils_Printf(MSG_NORMAL,

- "CAN_APP: Message Id Received %x Message Length is %u\t \n",

- CanIf_Mailbox->CanId, CanIf_PduInfoPtr->SduLength);

- for (loopCnt = 0U; loopCnt < CanIf_PduInfoPtr->SduLength;

- loopCnt++)

- {

- if (CanIf_PduInfoPtr->SduDataPtr[loopCnt] !=

- CanApp_InputData[loopCnt])

- {

- CanApp_TestPassed = E_NOT_OK;

- AppUtils_Printf(MSG_NORMAL,

- "CAN_APP: Transmitted and Received Data miss-match.\n");

- break;

- }

- else

- {

- CanApp_TestPassed = E_OK;

- }

- }

- AppUtils_Printf(MSG_NORMAL,

- "CAN_APP: Can Controller Instance MCAN %u \

-Internal LoopBack Mode Test Passed\n", ctlr_cnt);

- }

- else

- {

- CanApp_TestPassed = E_NOT_OK;

- break;

- }

-

-#if (CAN_LOOPBACK_ENABLE == STD_ON)

- Can_TestLoopBackModeDisable(

- CanConfigSet_CanController_List_PC[ctlr_cnt]->ControllerId, 0U);

-#endif

- if ((PduInfo->length == CanIf_PduInfoPtr->SduLength) &&

- (PduInfo->id == (CanIf_Mailbox->CanId | mask)))

- {

-#endif /* if defined SOC_AM62X) */

+ #if (STD_ON == GPT_ENABLE_DISABLE_NOTIFICATION_API)

+ Gpt_EnableNotification(chId);

+ AppUtils_Printf(MSG_NORMAL, "Can_Gpt: Enabled notification for channel [%d]\n", chId);

+ #endif

+ #if defined (SOC_J721E) || defined (SOC_J7200) || defined (SOC_J721S2) || defined (SOC_J784S4) || defined (SOC_J742S2)

+ countVal = GPTIMER_COUNT_VALUE_6_SEC_INPUT;

+ #endif

+ AppUtils_Printf(MSG_NORMAL, "Can_Gpt: Started Timer Channel [%d]\n", chId);

+ Gpt_StartTimer(chId, countVal);

- AppUtils_Printf(MSG_NORMAL,

- "CAN_APP: Message Id Received %x Message Length is %u\t \n",

- CanIf_Mailbox->CanId, CanIf_PduInfoPtr->SduLength);

- for (loopCnt = 0U; loopCnt < CanIf_PduInfoPtr->SduLength;

- loopCnt++)

- {

- if (CanIf_PduInfoPtr->SduDataPtr[loopCnt] !=

- CanApp_InputData[loopCnt])

- {

- CanApp_TestPassed = E_NOT_OK;

- AppUtils_Printf(MSG_NORMAL,

- "CAN_APP: Transmitted and Received Data miss-match.\n");

- break;

- }

- else

- {

- CanApp_TestPassed = E_OK;

- }

- }

- AppUtils_Printf(MSG_NORMAL,

- "CAN_APP: Can Controller Instance MCAN %u \

- Internal LoopBack Mode Test Passed\n", ctlr_cnt);

- }

- else

- {

- CanApp_TestPassed = E_NOT_OK;

- break;

- }

- }

+ while(1)

+ {

+ // if (chId == GptApp_NotifiedForInstFlag)

+ // {

+ // GptApp_NotifiedForInstFlag = 0xFFFF;

+ // BCAN_TX_0x3BA_APA1(txData);

+

+ // status = Can_Write(hth, PduInfo);

+ // if (status != E_OK)

+ // {

+ // AppUtils_Printf(MSG_NORMAL,

+ // "CAN_APP: Error In Can_Write.\n");

+ // CanApp_TestPassed = E_NOT_OK;

+ // }

+ // }

}

}

diff --git a/mcusw/mcal_drv/mcal/examples/Can/soc/j721s2/mcu1_0/CanApp_Startup.c b/mcusw/mcal_drv/mcal/examples/Can/soc/j721s2/mcu1_0/CanApp_Startup.c

index 76b55920..8b3c2f98 100755

--- a/mcusw/mcal_drv/mcal/examples/Can/soc/j721s2/mcu1_0/CanApp_Startup.c

+++ b/mcusw/mcal_drv/mcal/examples/Can/soc/j721s2/mcu1_0/CanApp_Startup.c

@@ -80,11 +80,23 @@ uint32 CanApp_InstanceSrcId[CAN_MAX_CONTROLLER];

CanApp_IsrType CanApp_Isr[CAN_MAX_CONTROLLER];

/**< Associated ISR */

uint32 CanApp_RoutIntNumbers[CAN_MAX_CONTROLLER];

+uint32 GptAppStartup_EnaTimer[APP_GPT_TOTAL_TIMER_COUNT];

+uint32 GptAppStartup_IntNumbers[APP_GPT_TOTAL_TIMER_COUNT];

+uint32 GptAppStartup_TimerSrcId[APP_GPT_TOTAL_TIMER_COUNT];

+uint32 GptAppStartup_RoutIntNumbers[APP_GPT_TOTAL_TIMER_COUNT];

+GptApp_IsrType GptAppStartup_Isr[APP_GPT_TOTAL_TIMER_COUNT];

+static void GptAppStartup_ClearAnyOperationalTimers(void);

+static void GptAppStartup_SetClockSource4Timers(void);

+static void GptAppStartup_InterruptConfig(void);

+

/**< Store the output interrupt number routed */

extern Can_PduType CanApp_Pdu, CanApp_Pdu1;

extern Can_PduType CanApp_Pdu2, CanApp_Pdu3, CanApp_Pdu4, CanApp_Pdu5;

/**< Variable used for copying protocol data unit */

extern uint8 CanApp_InputData[64U];

+extern uint8 txData[8U];

+extern const struct Gpt_ChannelConfigType_PC_s Gpt_ChannelConfig_PC[GPT_MAX_CHANNELS];

+

/**< Variables which contains Can PDU data used in Can transmission */

extern const Can_PduType *PduInfo;

/**< Variable which contains Can PDU data passed during Transmission */

@@ -99,6 +111,10 @@ void CanApp_Startup(void)

Intc_Init(); /* Interrupt handler initialized, here as other functions

* can use API's to clear pending interrupts if any

*/

+ GptAppStartup_ClearAnyOperationalTimers(); /* Clear MCU TIMER 0 only */

+ GptAppStartup_SetClockSource4Timers();

+ GptAppStartup_InterruptConfig();

+

CanApp_InterruptConfig();

/* Initialize counters, that would be required for timed operations */

@@ -109,10 +125,10 @@ void CanApp_Startup(void)

/* Message for CAN-FD(MCU MCAN0 module) */

/* Setting Up CAN FD Frame*/

- CanApp_Pdu.id = 0xA0 | 0x40000000U;

- CanApp_Pdu.length = 64U;

+ CanApp_Pdu.id = 0x3BA | 0x40000000U;

+ CanApp_Pdu.length = 8U;

CanApp_Pdu.swPduHandle = 1U;

- CanApp_Pdu.sdu = &CanApp_InputData[0U];

+ CanApp_Pdu.sdu = &txData[0U];

/* Message for CAN-FD(MCU MCAN1 module) */

/* Setting Up CAN FD Extended Frame*/

@@ -132,11 +148,14 @@ void CanApp_Startup(void)

void CanApp_BuildIntList(void)

{

- uint32 idx, flag, intNum;

+ uint32 idx, flag, intNum, timerDevId;

const Can_ConfigType *Can_ConfigPtr;

CanApp_IsrType pIsrHandler = NULL;

uint32 canMaxControllerCnt = 0U;

uint32 canDevId, routIntNum = 0U;

+ const Gpt_ChannelConfigType_PC *pChCfgPtr = NULL;

+ const Gpt_ConfigType *pCfgPtr = &GptChannelConfigSet;

+

/*

* 1. Determine the number of timers used

* 2. Build valid timer list

@@ -165,6 +184,265 @@ void CanApp_BuildIntList(void)

CanApp_RoutIntNumbers[idx] = 0U;

}

+ for (idx = 0U; idx < APP_GPT_TOTAL_TIMER_COUNT; idx++)

+ {

+ GptAppStartup_EnaTimer[idx] = 0U;

+ GptAppStartup_IntNumbers[idx] = 0U;

+ GptAppStartup_TimerSrcId[idx] = 0U;

+ }

+

+ for (idx = 0U; idx < pCfgPtr->channelCount; idx++)

+ {

+ pChCfgPtr = &Gpt_ChannelConfig_PC[idx];

+ flag = 0U;

+ routIntNum = 0U;

+ timerDevId = 0U;

+ switch(pChCfgPtr->channelId)

+ {

+#ifdef GptConf_GptChannelConfiguration_MCU_TIMER6

+ case GPT_CH_GPTIMER7:

+ intNum = APP_GPT_MCU_6_INT;

+ pIsrHandler = Gpt_Ch7Isr;

+ flag = 1U;

+ break;

+#endif

+#ifdef GptConf_GptChannelConfiguration_MCU_TIMER7

+ case GPT_CH_GPTIMER8:

+ intNum = APP_GPT_MCU_7_INT;

+ pIsrHandler = Gpt_Ch8Isr;

+ flag = 1U;

+ break;

+#endif

+#ifdef GptConf_GptChannelConfiguration_MCU_TIMER8

+ case GPT_CH_GPTIMER9:

+ intNum = APP_GPT_MCU_8_INT;

+ pIsrHandler = Gpt_Ch9Isr;

+ flag = 1U;

+ break;

+#endif

+#ifdef GptConf_GptChannelConfiguration_MCU_TIMER9

+ case GPT_CH_GPTIMER10:

+ intNum = APP_GPT_MCU_9_INT;

+ pIsrHandler = Gpt_Ch10Isr;

+ flag = 1U;

+ break;

+#endif

+#ifdef GptConf_GptChannelConfiguration_TIMER0

+ case GPT_CH_GPTIMER11:

+ intNum = APP_GPT_0_INT;

+ routIntNum = INTRTR_CFG_MAIN_DOMAIN_TIMER_1_OUT_INT_NO +

+ INTRTR_CFG_START_LEVEL_INT_NUMBER;

+ pIsrHandler = Gpt_Ch11Isr;

+ timerDevId = TISCI_DEV_TIMER0;

+ flag = 1U;

+ break;

+#endif

+#ifdef GptConf_GptChannelConfiguration_TIMER1

+ case GPT_CH_GPTIMER12:

+ intNum = APP_GPT_1_INT;

+ routIntNum = INTRTR_CFG_MAIN_DOMAIN_TIMER_2_OUT_INT_NO +

+ INTRTR_CFG_START_LEVEL_INT_NUMBER;

+ pIsrHandler = Gpt_Ch12Isr;

+ timerDevId = TISCI_DEV_TIMER1;

+ flag = 1U;

+ break;

+#endif

+#ifdef GptConf_GptChannelConfiguration_TIMER2

+ case GPT_CH_GPTIMER13:

+ intNum = APP_GPT_2_INT;

+ routIntNum = INTRTR_CFG_MAIN_DOMAIN_TIMER_3_OUT_INT_NO +

+ INTRTR_CFG_START_LEVEL_INT_NUMBER;

+ pIsrHandler = Gpt_Ch13Isr;

+ timerDevId = TISCI_DEV_TIMER2;

+ flag = 1U;

+ break;

+#endif

+#ifdef GptConf_GptChannelConfiguration_TIMER3

+ case GPT_CH_GPTIMER14:

+ intNum = APP_GPT_3_INT;

+ routIntNum = INTRTR_CFG_MAIN_DOMAIN_TIMER_4_OUT_INT_NO +

+ INTRTR_CFG_START_LEVEL_INT_NUMBER;

+ pIsrHandler = Gpt_Ch14Isr;

+ timerDevId = TISCI_DEV_TIMER3;

+ flag = 1U;

+ break;

+#endif

+#ifdef GptConf_GptChannelConfiguration_TIMER4

+ case GPT_CH_GPTIMER15:

+ intNum = APP_GPT_4_INT;

+ routIntNum = INTRTR_CFG_MAIN_DOMAIN_TIMER_5_OUT_INT_NO +

+ INTRTR_CFG_START_LEVEL_INT_NUMBER;

+ pIsrHandler = Gpt_Ch15Isr;

+ timerDevId = TISCI_DEV_TIMER4;

+ flag = 1U;

+ break;

+#endif

+#ifdef GptConf_GptChannelConfiguration_TIMER5

+ case GPT_CH_GPTIMER16:

+ intNum = APP_GPT_5_INT;

+ routIntNum = INTRTR_CFG_MAIN_DOMAIN_TIMER_6_OUT_INT_NO +

+ INTRTR_CFG_START_LEVEL_INT_NUMBER;

+ pIsrHandler = Gpt_Ch16Isr;

+ timerDevId = TISCI_DEV_TIMER5;

+ flag = 1U;

+ break;

+#endif

+#ifdef GptConf_GptChannelConfiguration_TIMER6

+ case GPT_CH_GPTIMER17:

+ intNum = APP_GPT_6_INT;

+ routIntNum = INTRTR_CFG_MAIN_DOMAIN_TIMER_7_OUT_INT_NO +

+ INTRTR_CFG_START_LEVEL_INT_NUMBER;

+ pIsrHandler = Gpt_Ch17Isr;

+ timerDevId = TISCI_DEV_TIMER6;

+ flag = 1U;

+ break;

+#endif

+#ifdef GptConf_GptChannelConfiguration_TIMER7

+ case GPT_CH_GPTIMER18:

+ intNum = APP_GPT_7_INT;

+ routIntNum = INTRTR_CFG_MAIN_DOMAIN_TIMER_8_OUT_INT_NO +

+ INTRTR_CFG_START_LEVEL_INT_NUMBER;

+ pIsrHandler = Gpt_Ch18Isr;

+ timerDevId = TISCI_DEV_TIMER7;

+ flag = 1U;

+ break;

+#endif

+#ifdef GptConf_GptChannelConfiguration_TIMER8

+ case GPT_CH_GPTIMER19:

+ intNum = APP_GPT_8_INT;

+ routIntNum = INTRTR_CFG_MAIN_DOMAIN_TIMER_9_OUT_INT_NO +

+ INTRTR_CFG_START_LEVEL_INT_NUMBER;

+ pIsrHandler = Gpt_Ch19Isr;

+ timerDevId = TISCI_DEV_TIMER8;

+ flag = 1U;

+ break;

+#endif

+#ifdef GptConf_GptChannelConfiguration_TIMER9

+ case GPT_CH_GPTIMER20:

+ intNum = APP_GPT_9_INT;

+ routIntNum = INTRTR_CFG_MAIN_DOMAIN_TIMER_10_OUT_INT_NO +

+ INTRTR_CFG_START_LEVEL_INT_NUMBER;

+ pIsrHandler = Gpt_Ch20Isr;

+ timerDevId = TISCI_DEV_TIMER9;

+ flag = 1U;

+ break;

+#endif

+#ifdef GptConf_GptChannelConfiguration_TIMER10

+ case GPT_CH_GPTIMER21:

+ intNum = APP_GPT_10_INT;

+ routIntNum = INTRTR_CFG_MAIN_DOMAIN_TIMER_11_OUT_INT_NO +

+ INTRTR_CFG_START_LEVEL_INT_NUMBER;

+ pIsrHandler = Gpt_Ch21Isr;

+ timerDevId = TISCI_DEV_TIMER10;

+ flag = 1U;

+ break;

+#endif

+#ifdef GptConf_GptChannelConfiguration_TIMER11

+ case GPT_CH_GPTIMER22:

+ intNum = APP_GPT_11_INT;

+ routIntNum = INTRTR_CFG_MAIN_DOMAIN_TIMER_12_OUT_INT_NO +

+ INTRTR_CFG_START_LEVEL_INT_NUMBER;

+ pIsrHandler = Gpt_Ch22Isr;

+ timerDevId = TISCI_DEV_TIMER11;

+ flag = 1U;

+ break;

+#endif

+#ifdef GptConf_GptChannelConfiguration_TIMER12

+ case GPT_CH_GPTIMER23:

+ intNum = APP_GPT_12_INT;

+ routIntNum = INTRTR_CFG_MAIN_DOMAIN_TIMER_13_OUT_INT_NO +

+ INTRTR_CFG_START_LEVEL_INT_NUMBER;

+ pIsrHandler = Gpt_Ch23Isr;

+ timerDevId = TISCI_DEV_TIMER12;

+ flag = 1U;

+ break;

+#endif

+#ifdef GptConf_GptChannelConfiguration_TIMER13

+ case GPT_CH_GPTIMER24:

+ intNum = APP_GPT_13_INT;

+ routIntNum = INTRTR_CFG_MAIN_DOMAIN_TIMER_14_OUT_INT_NO +

+ INTRTR_CFG_START_LEVEL_INT_NUMBER;

+ pIsrHandler = Gpt_Ch24Isr;

+ timerDevId = TISCI_DEV_TIMER13;

+ flag = 1U;

+ break;

+#endif

+#ifdef GptConf_GptChannelConfiguration_TIMER14

+ case GPT_CH_GPTIMER25:

+ intNum = APP_GPT_14_INT;

+ routIntNum = INTRTR_CFG_MAIN_DOMAIN_TIMER_15_OUT_INT_NO +

+ INTRTR_CFG_START_LEVEL_INT_NUMBER;

+ pIsrHandler = Gpt_Ch25Isr;

+ timerDevId = TISCI_DEV_TIMER14;

+ flag = 1U;

+ break;

+#endif

+#ifdef GptConf_GptChannelConfiguration_TIMER15

+ case GPT_CH_GPTIMER26:

+ intNum = APP_GPT_15_INT;

+ routIntNum = INTRTR_CFG_MAIN_DOMAIN_TIMER_16_OUT_INT_NO +

+ INTRTR_CFG_START_LEVEL_INT_NUMBER;

+ pIsrHandler = Gpt_Ch26Isr;

+ timerDevId = TISCI_DEV_TIMER15;

+ flag = 1U;

+ break;

+#endif

+#ifdef GptConf_GptChannelConfiguration_TIMER16

+ case GPT_CH_GPTIMER27:

+ intNum = APP_GPT_16_INT;

+ routIntNum = INTRTR_CFG_MAIN_DOMAIN_TIMER_17_OUT_INT_NO +

+ INTRTR_CFG_START_LEVEL_INT_NUMBER;

+ pIsrHandler = Gpt_Ch27Isr;

+ timerDevId = TISCI_DEV_TIMER16;

+ flag = 1U;

+ break;

+#endif

+#ifdef GptConf_GptChannelConfiguration_TIMER17

+ case GPT_CH_GPTIMER28:

+ intNum = APP_GPT_17_INT;

+ routIntNum = INTRTR_CFG_MAIN_DOMAIN_TIMER_18_OUT_INT_NO +

+ INTRTR_CFG_START_LEVEL_INT_NUMBER;

+ pIsrHandler = Gpt_Ch28Isr;

+ timerDevId = TISCI_DEV_TIMER17;

+ flag = 1U;

+ break;

+#endif

+#ifdef GptConf_GptChannelConfiguration_TIMER18

+ case GPT_CH_GPTIMER29:

+ intNum = APP_GPT_18_INT;

+ routIntNum = INTRTR_CFG_MAIN_DOMAIN_TIMER_19_OUT_INT_NO +

+ INTRTR_CFG_START_LEVEL_INT_NUMBER;

+ pIsrHandler = Gpt_Ch29Isr;

+ timerDevId = TISCI_DEV_TIMER18;

+ flag = 1U;

+ break;

+#endif

+#ifdef GptConf_GptChannelConfiguration_TIMER19

+ case GPT_CH_GPTIMER30:

+ intNum = APP_GPT_19_INT;

+ routIntNum = INTRTR_CFG_MAIN_DOMAIN_TIMER_20_OUT_INT_NO +

+ INTRTR_CFG_START_LEVEL_INT_NUMBER;

+ pIsrHandler = Gpt_Ch30Isr;

+ timerDevId = TISCI_DEV_TIMER19;

+ flag = 1U;

+ break;

+#endif

+ default:

+ AppUtils_Printf(MSG_NORMAL, "Can_Gpt: ERROR Interrupt registration is not done for timer ID %d !!!\n", pChCfgPtr->channelId);

+ flag = 0U;

+ break;

+ }

+ if (0U != flag)

+ {

+ GptAppStartup_EnaTimer[pChCfgPtr->channelId] = 1U;

+ GptAppStartup_IntNumbers[pChCfgPtr->channelId] = intNum;

+ GptAppStartup_RoutIntNumbers[pChCfgPtr->channelId] = routIntNum;

+ GptAppStartup_TimerSrcId[pChCfgPtr->channelId] = timerDevId;

+ GptAppStartup_Isr[pChCfgPtr->channelId] = pIsrHandler;

+ flag = 0U;

+ }

+ }

+

for (idx = 0U; idx < canMaxControllerCnt; idx++)

{

flag = 0U;

@@ -208,6 +486,150 @@ void CanApp_BuildIntList(void)

return;

}

+static void GptAppStartup_InterruptConfig(void)

+{

+ uint32 idx;

+ OsalRegisterIntrParams_t intrPrms;

+ OsalInterruptRetCode_e osalRetVal;

+ HwiP_Handle hwiHandle;

+ struct tisci_msg_rm_irq_set_req rmIrqReq;

+ struct tisci_msg_rm_irq_set_resp rmIrqResp;

+ Int32 retVal;

+

+ for (idx = 0U; idx < APP_GPT_TOTAL_TIMER_COUNT; idx++)

+ {

+ if (0U != GptAppStartup_EnaTimer[idx])

+ {

+ if (0U != GptAppStartup_RoutIntNumbers[idx])

+ {

+ /* We will have to use the routed interrupt number

+ subsequently */

+ GptAppStartup_IntNumbers[idx] = GptAppStartup_RoutIntNumbers[idx];

+

+ /* If the timer is not in MCU domain, the interrupt router will

+ have to be configured */

+ /* Set the destination interrupt */

+ rmIrqReq.valid_params = TISCI_MSG_VALUE_RM_DST_ID_VALID;

+ rmIrqReq.valid_params |= TISCI_MSG_VALUE_RM_DST_HOST_IRQ_VALID;

+ rmIrqReq.src_id = GptAppStartup_TimerSrcId[idx];

+ rmIrqReq.global_event = 0U;

+ rmIrqReq.src_index = 0U;

+ rmIrqReq.dst_id = TISCI_DEV_MCU_R5FSS0_CORE0;

+ rmIrqReq.dst_host_irq = GptAppStartup_RoutIntNumbers[idx];

+ rmIrqReq.ia_id = 0U;

+ rmIrqReq.vint = 0U;

+ rmIrqReq.vint_status_bit_index = 0U;

+ rmIrqReq.secondary_host = TISCI_MSG_VALUE_RM_UNUSED_SECONDARY_HOST;

+

+ retVal = Sciclient_rmIrqSet(

+ &rmIrqReq, &rmIrqResp, APP_SCICLIENT_TIMEOUT);

+ AppUtils_Printf(MSG_NORMAL, "Can_Gpt: rmIrqReq = %d\n",rmIrqReq);

+ // AppUtils_Printf(MSG_NORMAL,APP_NAME ": rmIrqResp = %d\n",rmIrqResp);

+ if(LLD_PASS != retVal)

+ {

+ AppUtils_Printf(MSG_NORMAL, "Can_Gpt: Error in SciClient Interrupt Params Configuration!!!\n");

+ }

+ }

+ Osal_RegisterInterrupt_initParams(&intrPrms);

+ intrPrms.corepacConfig.arg = (uintptr_t)GptAppStartup_Isr[idx];

+ intrPrms.corepacConfig.isrRoutine = &GptApp_GptXIsr;

+ intrPrms.corepacConfig.priority = 1U;

+ intrPrms.corepacConfig.corepacEventNum = 0U; /* NOT USED ? */

+ intrPrms.corepacConfig.intVecNum = GptAppStartup_IntNumbers[idx];

+

+ osalRetVal = Osal_RegisterInterrupt(&intrPrms, &hwiHandle);

+ if(OSAL_INT_SUCCESS != osalRetVal)

+ {

+ AppUtils_Printf(MSG_NORMAL, "Can_Gpt: Error in OSAL Interrupt Registration !!!\n");

+ break;

+ }

+ }

+ }

+

+ return;

+}

+

+static void GptAppStartup_SetClockSource4Timers(void)

+{

+#ifdef NOT_YET

+/* The MMR has been fire walled, use SciClient to configure the clock source.

+ * Use of Sciclient is not demonstrated in MCAL examples at this point

+ */

+

+ uint32 idx;

+

+ /* Un Lock MMR for MCU control MMR */

+ HW_WR_REG32_RAW(

+ (CSL_MCU_CTRL_MMR0_CFG0_BASE + CSL_MCU_CTRL_MMR_CFG0_LOCK0_KICK0),

+ 0x68EF3490);

+ HW_WR_REG32_RAW(

+ (CSL_MCU_CTRL_MMR0_CFG0_BASE + CSL_MCU_CTRL_MMR_CFG0_LOCK0_KICK1),

+ 0xD172BC5A);

+

+ for (idx = 0U; idx < APP_GPT_TOTAL_TIMER_COUNT; idx++)

+ {

+ if (0U != GptAppStartup_EnaTimer[idx])

+ {

+ if (idx < GPT_CH_GPTIMER5)

+ {

+ /* MCU Timers, 12.5 MHz clock to be sourced */

+ HW_WR_REG32_RAW((CSL_MCU_CTRL_MMR0_CFG0_BASE +

+ CSL_MCU_CTRL_MMR_CFG0_MCU_TIMER0_CLKSEL +

+ (idx * 0x04)),

+ 2U);

+ }

+ }

+ }

+

+#endif

+

+ return;

+}

+

+/** \brief Clear MCU TIMER 0 Timer */

+static void GptAppStartup_ClearAnyOperationalTimers(void)

+{

+ /* MCU Timer 0 is turned on by RBL and interrupts are enabled. We would

+ * require to disable the interrupt and clear MCU timer, to ensure no

+ * un-expected interrupts are received

+ * Steps

+ * 1. Disable the interrupt in MCU TIMER 0

+ * 2. Stop the timer

+ * 3. Enable Soft Reset

+ * 4. Reset the timer

+ * 5. Clear the interrupt in VIM of R5F

+ * 6. Reset the clock source

+ */

+ /* Steps 1 to 2 */

+ HW_WR_REG32_RAW((CSL_MCU_TIMER0_CFG_BASE + TIMER_IRQENABLE_CLR),

+ (TIMER_IRQENABLE_CLR_TCAR_EN_FLAG_MASK |

+ TIMER_IRQENABLE_CLR_OVF_EN_FLAG_MASK |

+ TIMER_IRQENABLE_CLR_MAT_EN_FLAG_MASK));

+ HW_WR_REG32_RAW((CSL_MCU_TIMER0_CFG_BASE + TIMER_TCLR), 0x0U);

+ /* Steps 3 to 4 */

+ HW_WR_REG32_RAW((CSL_MCU_TIMER0_CFG_BASE + TIMER_TSICR),

+ TIMER_TSICR_SFT_MASK);

+ HW_WR_REG32_RAW((CSL_MCU_TIMER0_CFG_BASE + TIMER_TIOCP_CFG),

+ TIMER_TIOCP_CFG_SOFTRESET_MASK);

+

+ /* Step 5 */

+ Intc_IntClrPend(APP_GPT_MCU_0_INT);

+

+ /* Step 6. Reset the clock source also */

+ /* Un Lock */

+ HW_WR_REG32_RAW(

+ (CSL_MCU_CTRL_MMR0_CFG0_BASE + CSL_MCU_CTRL_MMR_CFG0_LOCK0_KICK0),

+ 0x68EF3490);

+ HW_WR_REG32_RAW(

+ (CSL_MCU_CTRL_MMR0_CFG0_BASE + CSL_MCU_CTRL_MMR_CFG0_LOCK0_KICK1),

+ 0xD172BC5A);

+

+ /* Reset Clock source */

+ HW_WR_REG32_RAW((CSL_MCU_CTRL_MMR0_CFG0_BASE +

+ CSL_MCU_CTRL_MMR_CFG0_MCU_TIMER0_CLKSEL),

+ 0U /* Reset Value */);

+}

+

void CanApp_PlatformInit()

{

uint32 regVal = 0U;

diff --git a/mcusw/mcal_drv/mcal/examples/Can/soc/j721s2/mcu1_0/CanApp_Startup.h b/mcusw/mcal_drv/mcal/examples/Can/soc/j721s2/mcu1_0/CanApp_Startup.h

index 6686b312..e8f674f3 100755

--- a/mcusw/mcal_drv/mcal/examples/Can/soc/j721s2/mcu1_0/CanApp_Startup.h

+++ b/mcusw/mcal_drv/mcal/examples/Can/soc/j721s2/mcu1_0/CanApp_Startup.h

@@ -75,9 +75,12 @@

#include "CanIf_Cbk.h"

#include "EcuM_Cbk.h"

#include "Dio.h"

+#include "Gpt.h"

#include "app_utils.h"

+#include <hw_include/hw_types.h>

+#include <hw_include/lldr_timer.h>

#include <hw_include/soc.h>

#include <hw_include/lldr.h>

#include <hw_include/lld_types.h>

@@ -126,9 +129,81 @@

#define APP_MCAN_4_INT0 (CSLR_MAIN2MCU_LVL_INTRTR0_IN_MCAN4_MCANSS_MCAN_LVL_INT_0)

#define APP_MCAN_9_INT0 (CSLR_MAIN2MCU_LVL_INTRTR0_IN_MCAN9_MCANSS_MCAN_LVL_INT_0)

#define APP_MCAN_11_INT0 (CSLR_MAIN2MCU_LVL_INTRTR0_IN_MCAN11_MCANSS_MCAN_LVL_INT_0)

+#define GPTIMER_COUNT_VALUE_6_SEC_INPUT (4026530) ///402653

+#define APP_GPT_TOTAL_TIMER_COUNT (30U)

+

+

+#define APP_GPT_MCU_0_INT (CSLR_MCU_R5FSS0_CORE0_INTR_MCU_TIMER0_INTR_PEND_0)

+#define APP_GPT_MCU_1_INT (CSLR_MCU_R5FSS0_CORE0_INTR_MCU_TIMER1_INTR_PEND_0)

+#define APP_GPT_MCU_2_INT (CSLR_MCU_R5FSS0_CORE0_INTR_MCU_TIMER2_INTR_PEND_0)

+#define APP_GPT_MCU_3_INT (CSLR_MCU_R5FSS0_CORE0_INTR_MCU_TIMER3_INTR_PEND_0)

+#define APP_GPT_MCU_4_INT (CSLR_MCU_R5FSS0_CORE0_INTR_MCU_TIMER4_INTR_PEND_0)

+#define APP_GPT_MCU_5_INT (CSLR_MCU_R5FSS0_CORE0_INTR_MCU_TIMER5_INTR_PEND_0)

+#define APP_GPT_MCU_6_INT (CSLR_MCU_R5FSS0_CORE0_INTR_MCU_TIMER6_INTR_PEND_0)

+#define APP_GPT_MCU_7_INT (CSLR_MCU_R5FSS0_CORE0_INTR_MCU_TIMER7_INTR_PEND_0)

+#define APP_GPT_MCU_8_INT (CSLR_MCU_R5FSS0_CORE0_INTR_MCU_TIMER8_INTR_PEND_0)

+#define APP_GPT_MCU_9_INT (CSLR_MCU_R5FSS0_CORE0_INTR_MCU_TIMER9_INTR_PEND_0)

+#define APP_GPT_0_INT (CSLR_MAIN2MCU_LVL_INTRTR0_IN_TIMER0_INTR_PEND_0)

+#define APP_GPT_1_INT (CSLR_MAIN2MCU_LVL_INTRTR0_IN_TIMER1_INTR_PEND_0)

+#define APP_GPT_2_INT (CSLR_MAIN2MCU_LVL_INTRTR0_IN_TIMER2_INTR_PEND_0)

+#define APP_GPT_3_INT (CSLR_MAIN2MCU_LVL_INTRTR0_IN_TIMER3_INTR_PEND_0)

+#define APP_GPT_4_INT (CSLR_MAIN2MCU_LVL_INTRTR0_IN_TIMER4_INTR_PEND_0)

+#define APP_GPT_5_INT (CSLR_MAIN2MCU_LVL_INTRTR0_IN_TIMER5_INTR_PEND_0)

+#define APP_GPT_6_INT (CSLR_MAIN2MCU_LVL_INTRTR0_IN_TIMER6_INTR_PEND_0)

+#define APP_GPT_7_INT (CSLR_MAIN2MCU_LVL_INTRTR0_IN_TIMER7_INTR_PEND_0)

+#define APP_GPT_8_INT (CSLR_MAIN2MCU_LVL_INTRTR0_IN_TIMER8_INTR_PEND_0)

+#define APP_GPT_9_INT (CSLR_MAIN2MCU_LVL_INTRTR0_IN_TIMER9_INTR_PEND_0)

+#define APP_GPT_10_INT (CSLR_MAIN2MCU_LVL_INTRTR0_IN_TIMER10_INTR_PEND_0)

+#define APP_GPT_11_INT (CSLR_MAIN2MCU_LVL_INTRTR0_IN_TIMER11_INTR_PEND_0)

+#define APP_GPT_12_INT (CSLR_MAIN2MCU_LVL_INTRTR0_IN_TIMER12_INTR_PEND_0)

+#define APP_GPT_13_INT (CSLR_MAIN2MCU_LVL_INTRTR0_IN_TIMER13_INTR_PEND_0)

+#define APP_GPT_14_INT (CSLR_MAIN2MCU_LVL_INTRTR0_IN_TIMER14_INTR_PEND_0)

+#define APP_GPT_15_INT (CSLR_MAIN2MCU_LVL_INTRTR0_IN_TIMER15_INTR_PEND_0)

+#define APP_GPT_16_INT (CSLR_MAIN2MCU_LVL_INTRTR0_IN_TIMER16_INTR_PEND_0)

+#define APP_GPT_17_INT (CSLR_MAIN2MCU_LVL_INTRTR0_IN_TIMER17_INTR_PEND_0)

+#define APP_GPT_18_INT (CSLR_MAIN2MCU_LVL_INTRTR0_IN_TIMER18_INTR_PEND_0)

+#define APP_GPT_19_INT (CSLR_MAIN2MCU_LVL_INTRTR0_IN_TIMER19_INTR_PEND_0)

+

+typedef union

+{

+ uint64 U64;

+ uint32 U32[2];

+ uint16 U16[4];

+ uint8 U08[8];

+

+ struct

+ {

+ uint8 APA_Rq_EPS_Ctrl :1;

+ uint8 APA_V_Rq_EPS_Ctrl :1;

+ uint8 ResBits00 :6;

+

+ uint8 APA_Angle_Target_0;

+ uint8 APA_Angle_Target_1;

+ uint8 ResByte3;

+ uint8 ResByte4;

+

+ uint8 APA_checksum :4;

+ uint8 APA_Roll_Count :4;

+

+ uint8 ResByte6;

+ uint8 ResByte7;

+ } Bits;

+

+} TU_APA1_MSG;

+

+struct {

+ struct {

+ struct {

+ uint8 Valid;

+ uint8 Apply;

+ uint16 Value;

+ } Angle;

+ } TX;

+} bcanData;

void CanApp_CanXIsr(uintptr_t CanPtr);

typedef void (*CanApp_IsrType)(void);

+typedef void (*GptApp_IsrType)(void);

/* ========================================================================== */

/* Internal Function Declarations */

@@ -143,4 +218,7 @@ void SetupI2CTransfer(I2C_Handle handle, uint32 slaveAddr,

uint8 *writeData, uint32 numWriteBytes,

uint8 *readData, uint32 numReadBytes);

void CanApp_SetupCanFrame(uint32 ctlr_cnt, uint8 *hth, uint32 *mask);

+#if defined (SOC_J721E) || (SOC_J7200) || (SOC_J721S2) || defined (SOC_J784S4) || defined (SOC_J742S2)

+void GptApp_GptXIsr(uintptr_t GptPtr);

+#endif

#endif /* CANAPP_STARTUP_H_ */

diff --git a/mcusw/mcal_drv/mcal/examples_config/Can_Demo_Cfg/output/generated/soc/j721s2/mcu1_0/src/Can_Cfg.c b/mcusw/mcal_drv/mcal/examples_config/Can_Demo_Cfg/output/generated/soc/j721s2/mcu1_0/src/Can_Cfg.c

index c24e93e0..e9c47f5f 100644

--- a/mcusw/mcal_drv/mcal/examples_config/Can_Demo_Cfg/output/generated/soc/j721s2/mcu1_0/src/Can_Cfg.c

+++ b/mcusw/mcal_drv/mcal/examples_config/Can_Demo_Cfg/output/generated/soc/j721s2/mcu1_0/src/Can_Cfg.c

@@ -97,13 +97,13 @@

static Can_BaudConfigType

CanConfigSet_CanController_0_CanControllerBaudrateConfig_0 =

{

- 1000U, /* in Kbps */

+ 500U, /* in Kbps */

8U, /* Prop Segement value */

6U, /* Phase Segment 1 */

5U, /* Phase Segment 2 */

1U, /* Sync jump width */

20U, /* Sum of all timing parameters */

- 4U, /* Controller BRP value for Baud */

+ 8U, /* Controller BRP value for Baud */

/* Data phase Baudrate */

{

5000U, /* in Kbps */

@@ -114,7 +114,7 @@ static Can_BaudConfigType

5U, /* Sum of all timing parameters */

4U, /* Controller BRP value for Baud */

180U, /* Specifies the Transceiver Delay Compensation Offset in ns */

- (boolean)TRUE, /* Specifies if the bit rate switching shall be used */

+ (boolean)FALSE, /* Specifies if the bit rate switching shall be used */

}

};

static Can_BaudConfigType

@@ -221,7 +221,7 @@ const struct Can_ControllerStruct_PC

CAN_CONTROLLER_INSTANCE_MCU_MCAN0, /* Controller Instance */

- (boolean)TRUE, /* CAN FD Mode Enable */

+ (boolean)FALSE, /* CAN FD Mode Enable */

};

const struct Can_ControllerStruct_PC

CanConfigSet_PC_CanController_1 =

@@ -237,7 +237,7 @@ const struct Can_ControllerStruct_PC

CAN_CONTROLLER_INSTANCE_MCU_MCAN1, /* Controller Instance */

- (boolean)TRUE, /* CAN FD Mode Enable */

+ (boolean)FALSE, /* CAN FD Mode Enable */

};

const struct Can_ControllerStruct_PC

CanConfigSet_PC_CanController_2 =

@@ -253,7 +253,7 @@ const struct Can_ControllerStruct_PC

CAN_CONTROLLER_INSTANCE_MCAN0, /* Controller Instance */

- (boolean)TRUE, /* CAN FD Mode Enable */

+ (boolean)FALSE, /* CAN FD Mode Enable */

};

@@ -350,7 +350,7 @@ static Can_MailboxType

&CanConfigSet_PC_CanController_0, /* Controller */

NULL_PTR, /* List of HW Filter structs */

0U, /* Hw Filter Count */

- 204U, /* Padding value for CAN FD message */

+ 0U, /* Padding value for CAN FD message */

(boolean)FALSE, /* CanHardwareObjectUsesPolling */

};

@@ -367,7 +367,7 @@ static Can_MailboxType

&CanConfigSet_PC_CanController_0, /* Controller */

NULL_PTR, /* List of HW Filter structs */

0U, /* Hw Filter Count */

- 204U, /* Padding value for CAN FD message */

+ 0U, /* Padding value for CAN FD message */

(boolean)FALSE, /* CanHardwareObjectUsesPolling */

};

@@ -384,7 +384,7 @@ static Can_MailboxType

&CanConfigSet_PC_CanController_1, /* Controller */

NULL_PTR, /* List of HW Filter structs */

0U, /* Hw Filter Count */

- 204U, /* Padding value for CAN FD message */

+ 0U, /* Padding value for CAN FD message */

(boolean)FALSE, /* CanHardwareObjectUsesPolling */

};

diff --git a/mcusw/mcal_drv/mcal/examples_config/Gpt_Demo_Cfg/output/generated/soc/j721s2/mcu1_0/src/Gpt_PBcfg.c b/mcusw/mcal_drv/mcal/examples_config/Gpt_Demo_Cfg/output/generated/soc/j721s2/mcu1_0/src/Gpt_PBcfg.c

index 762d7300..70c1cc2e 100644

--- a/mcusw/mcal_drv/mcal/examples_config/Gpt_Demo_Cfg/output/generated/soc/j721s2/mcu1_0/src/Gpt_PBcfg.c

+++ b/mcusw/mcal_drv/mcal/examples_config/Gpt_Demo_Cfg/output/generated/soc/j721s2/mcu1_0/src/Gpt_PBcfg.c

@@ -117,11 +117,11 @@ static CONST(Gpt_ChannelConfigType, GPT_CONFIG_DATA)

[0U] =

{

- .channelMode = (GPT_CH_MODE_ONESHOT),

+ .channelMode = (GPT_CH_MODE_CONTINUOUS),

/**< Gpt Channel Mode */

.tickValueMax = 0xf0000000U,

/**< Max Channel Tick Value */

- .enableWakeupFlag = (uint8) TRUE,

+ .enableWakeupFlag = (uint8) FALSE,

/**< Wakeup Enable Flag */

.fnPtrNotifyFunction = Gpt_Channel_Notify12,

/**< Notification Call Back function */

log:

CAN_APP: Sample Application - STARTS !!!

CAN_APP: Variant - Pre Compile being used !!!

Can_Gpt: rmIrqReq = 2

Can_Gpt: rmIrqReq = 2

Can_Gpt: rmIrqReq = 2

CAN_APP: Successfully Enabled CAN Transceiver MCU MCAN0!!!

CAN_APP: Successfully Enabled CAN Transceiver MCU MCAN1!!!

Can_Gpt: Enabled notification for channel [6]

Can_Gpt: Started Timer Channel [6]

CCS screenshot:

CAN sent message:

Many thanks!!

Alice