Tool/software:

Hello,

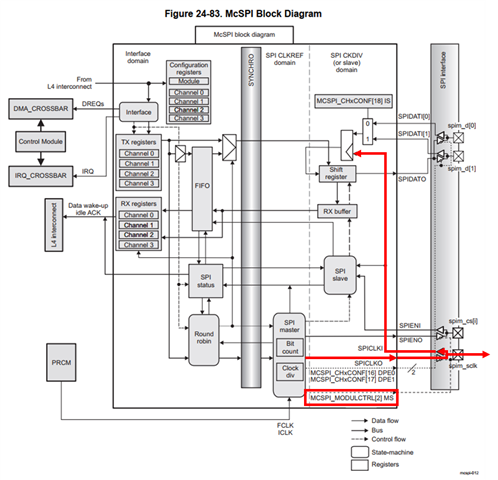

I'm working with the AM5728 and facing an issue where MCSPI1 always reads 0x00 from the MISO pin (SPI1_D1), even though the slave device is sending data correctly.

1. PAD Configuration

CTRL_CORE_PAD_SPI1_D1 (F16) = 0x00040000

CTRL_CORE_PAD_SPI1_D0 (B25) = 0x00010000

CTRL_CORE_PAD_SPI1_CLK (A25) = 0x00010000

CTRL_CORE_PAD_SPI1_CS0 (A24) = 0x00010000

2. MCSPI Register Settings

MCSPI_MODULCTRL = 0x00000001

MCSPI_CHxCONF = 0x181E0FC0

Observations

-

The slave correctly receives data via MOSI.

-

An oscilloscope shows valid data on the MISO line.

-

However, when I read from MCSPI1 RX register, all values are 0x00.

Could you please help me understand what might be missing or misconfigured?

Thanks in advance.