Other Parts Discussed in Thread: SK-AM69, TDA4VH, AM69

Tool/software:

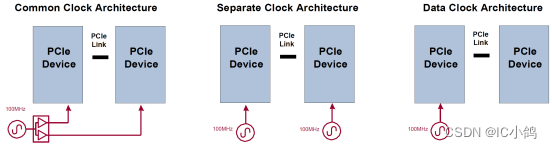

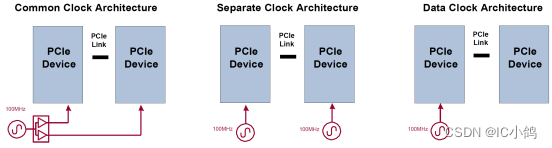

Our custom board PCIe Root configuration as below:

PCIE0 (SERDES1 LANE0 LANE1 LANE2 LANE3),

PCIE1 (SERDES0 LANE0/LANE1)

PCIE3 (SERDES0 LANE2/LANE3)

FPGA side 3 port are PCIe EP.

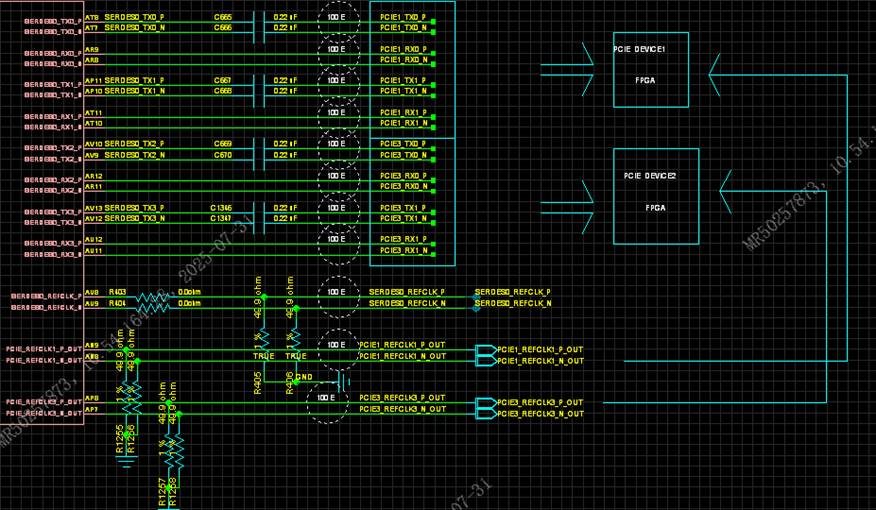

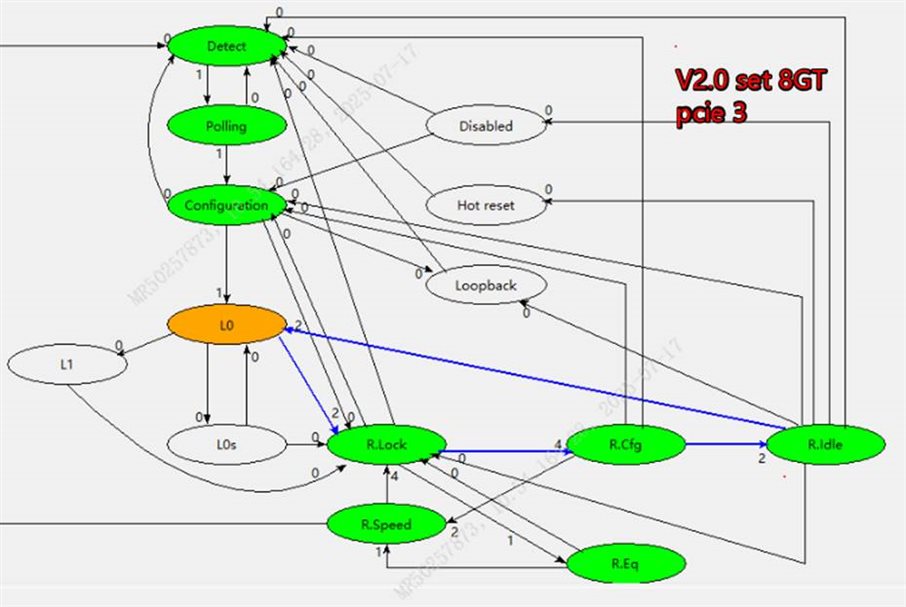

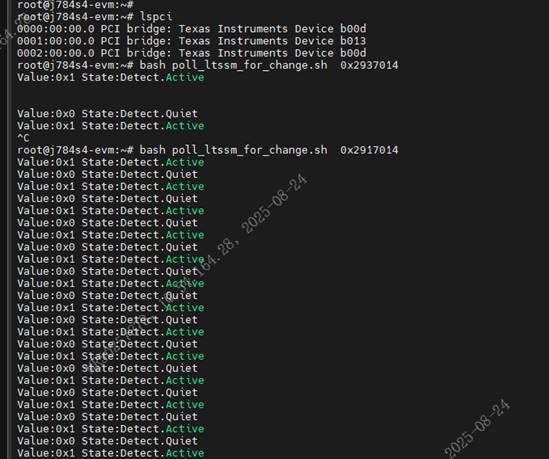

When 3 EP (FPGA) connected and configured at 8GT/s, PCIe3 can't be recognized, PCIE0 /PCIE1 can be recognized and run at 8GT/s

When 3 EP configured at 5GT/s, all can be recognized and run at 5GT/s..

If only connect PCIe and configure EP at 8GT/s, PCIe3 can be recognized but only run at 2.5GT/s.

Question : Can PCIE1 and PCIE3 operate at 8GT/s at the same time on one Serdes0?