Other Parts Discussed in Thread: AM67,

Tool/software:

Hi,

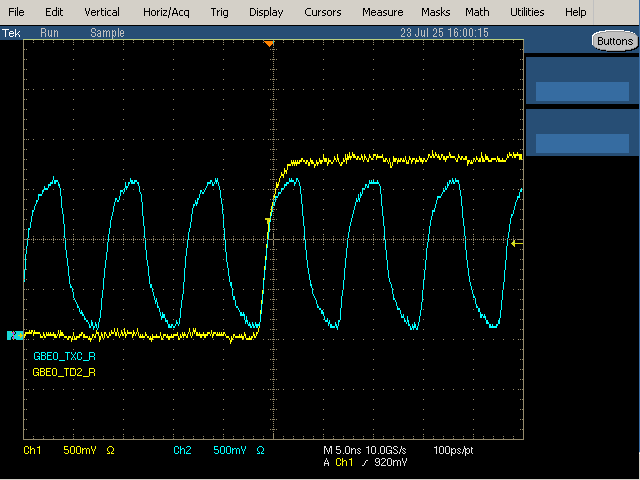

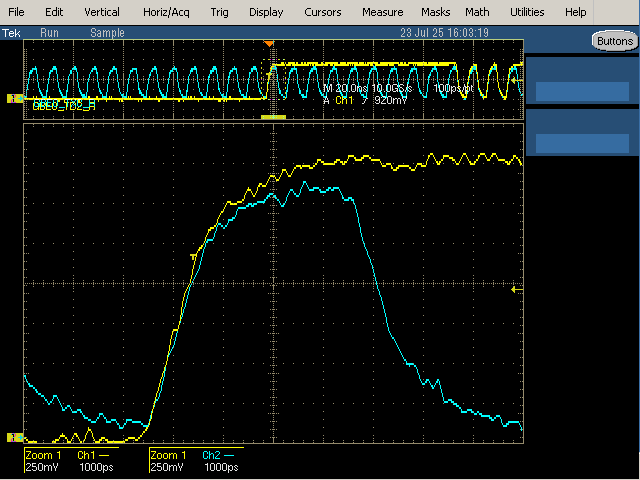

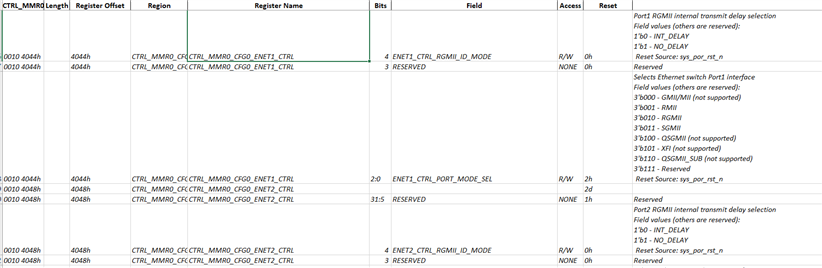

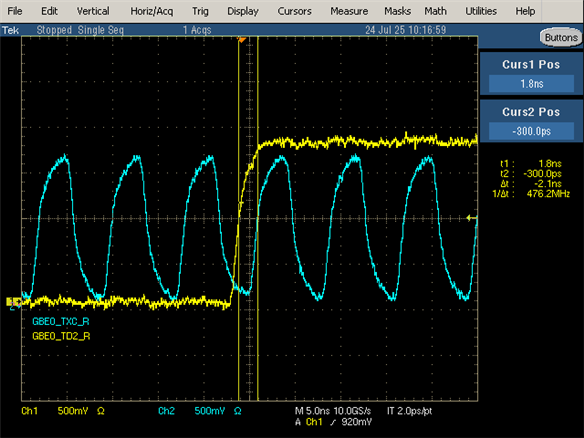

according to the datasheet, there should be an internal RGMII delay on the TX path towards the PHY. We cannot measure this delay though. Can you confirm, that there actually is a delay on the TX path?

I'm asking because the network transmit path stops working if I disable the delay in the PHY (which should not be needed because of the fixed delay of the SoC).

Thanks,

-michael