Tool/software:

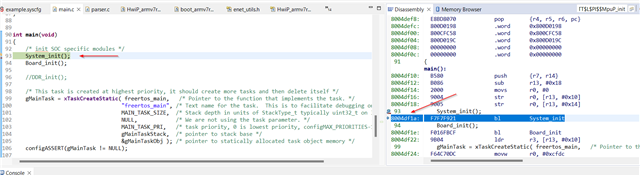

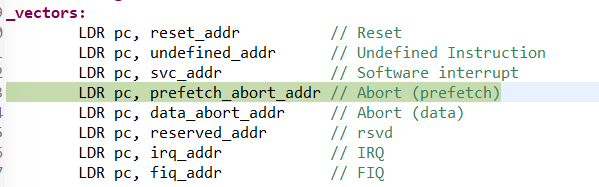

I'm currently experimenting with the AM6442 EVM board using CCS. I'm trying to get an example project (FreeRTOS based) from the MCU+ SDK v10.01, which I've enhanced, to run from DDR on the R5F0_1 Core as I've exceeded the MSRAM space. The project builds fine, but when I load it to the Core in the XDS110 Debug interface I get nothing. The program is in run state, breakpoints dont hit, when I suspend it is stuck in a prefetch_abort_addr call in HwiP_armv7r_vectors_freertos_asm:

So far in my research I followed the SoC Peripheral Drivers --> DDR part of the SDK help files to create and load the board_ddrReginit.h file, but haven't found anything else specific which is helping.

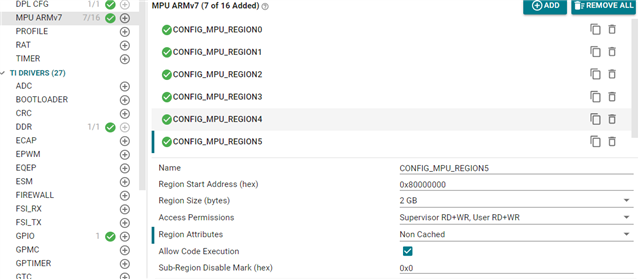

Any help on this matter would be greatly appreciated, my syscfg and linker information is as follows:

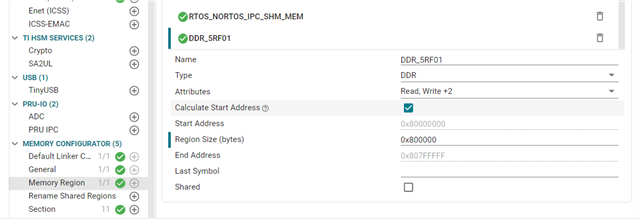

syscfg settings related to DDR:

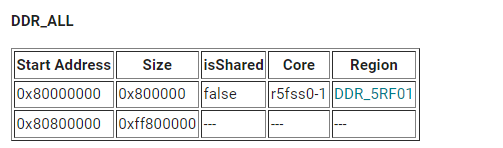

The Memory Summary shows:

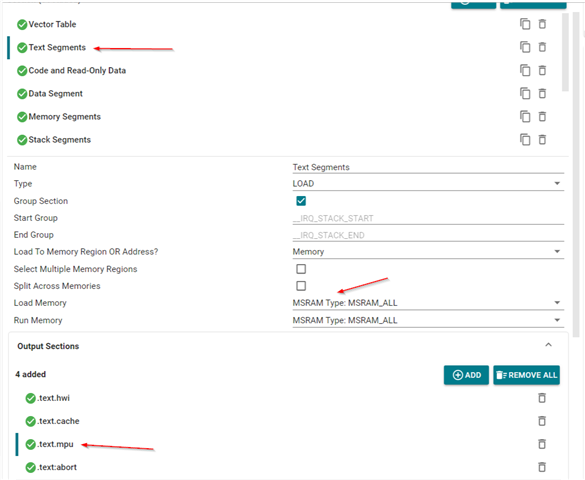

My modifications to the Memory Configurator->Section result in the following in my linker.cmd file:

SECTIONS

{

.vectors : {

} > R5F_VECS , palign(8)

GROUP : {

.text.hwi : {

} palign(8)

.text.cache : {

} palign(8)

.text.mpu : {

} palign(8)

.text:abort : {

} palign(8)

} > DDR_5RF01

GROUP : {

.text : {

} palign(8)

.rodata : {

} palign(8)

} > DDR_5RF01

GROUP : {

.data : {

} palign(8)

} > DDR_5RF01

GROUP : {

.bss : {

} palign(8)

RUN_START(__BSS_START)

RUN_END(__BSS_END)

.sysmem : {

} palign(8)

.stack : {

} palign(8)

} > DDR_5RF01

GROUP : {

.irqstack : {

. = . + __IRQ_STACK_SIZE;

} align(8)

RUN_START(__IRQ_STACK_START)

RUN_END(__IRQ_STACK_END)

.fiqstack : {

. = . + __FIQ_STACK_SIZE;

} align(8)

RUN_START(__FIQ_STACK_START)

RUN_END(__FIQ_STACK_END)

.svcstack : {

. = . + __SVC_STACK_SIZE;

} align(8)

RUN_START(__SVC_STACK_START)

RUN_END(__SVC_STACK_END)

.abortstack : {

. = . + __ABORT_STACK_SIZE;

} align(8)

RUN_START(__ABORT_STACK_START)

RUN_END(__ABORT_STACK_END)

.undefinedstack : {

. = . + __UNDEFINED_STACK_SIZE;

} align(8)

RUN_START(__UNDEFINED_STACK_START)

RUN_END(__UNDEFINED_STACK_END)

} > MSRAM

GROUP : {

.ARM.exidx : {

} palign(8)

.init_array : {

} palign(8)

.fini_array : {

} palign(8)

.text.boot : {

} palign(8)

} > MSRAM

.bss.user_shared_mem (NOLOAD) : {

} > USER_SHM_MEM

.bss.log_shared_mem (NOLOAD) : {

} > LOG_SHM_MEM

.bss.ipc_vring_mem (NOLOAD) : {

} > RTOS_NORTOS_IPC_SHM_MEM

.bss.nocache (NOLOAD) : {

} > MSRAM

}

MEMORY

{

R5F_VECS : ORIGIN = 0x0 , LENGTH = 0x40

R5F_TCMA : ORIGIN = 0x40 , LENGTH = 0x7FC0

R5F_TCMB0 : ORIGIN = 0x41010000 , LENGTH = 0x8000

NON_CACHE_MEM : ORIGIN = 0x70040000 , LENGTH = 0x8000

MSRAM : ORIGIN = 0x70000000 , LENGTH = 0x40000

USER_SHM_MEM : ORIGIN = 0x70050000 , LENGTH = 0x4000

LOG_SHM_MEM : ORIGIN = 0x70054000 , LENGTH = 0x4000

RTOS_NORTOS_IPC_SHM_MEM : ORIGIN = 0x70048000 , LENGTH = 0x8000

FLASH : ORIGIN = 0x60180000 , LENGTH = 0x80000

DDR_5RF01 : ORIGIN = 0x80000000 , LENGTH = 0x800000

}