Tool/software:

Hi, TI Expert

I try to study how to reduce the clock speed of the MCU M4F PLL

Two question,

(1) Do we have SW API (MCU SDK) to change MCU M4F PLL, and Do we have any example code?

(2) Does it support "dynamic" change MCU M4F PLL in MCU code.

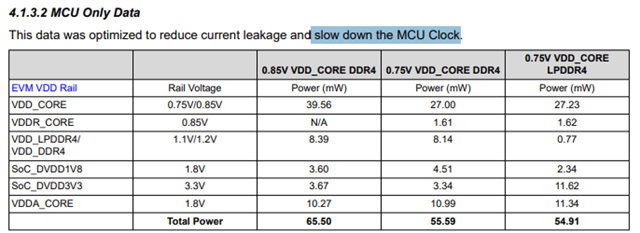

(3) What's MCU clock in below table? (MCU LPM)

Because I try to reduce MCU speed to save more power in PCU LPM.

Thank You.

Gibbs