Tool/software:

Subject:

Illegal Instruction (ESR_EL1=0x02000000) on Cortex-A53 During Warm Boot at 0x80001180(ELR_EL1 =0x80001180) - Root Cause Analysis and Mitigation

Environment:

Board: AM64B-GP/SK

SDK: mcu_plus_sdk_am64x_11_00_00_15

1. Symptom

- Scenario:

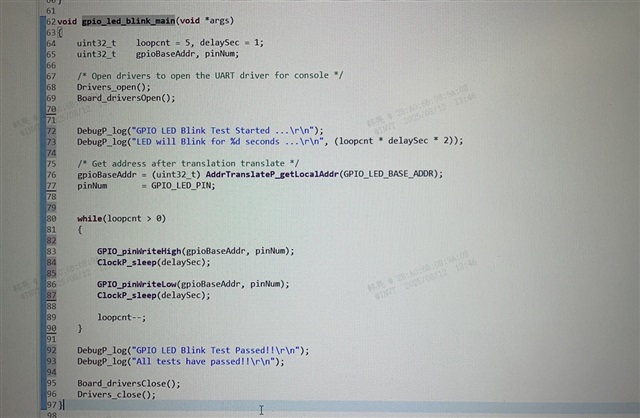

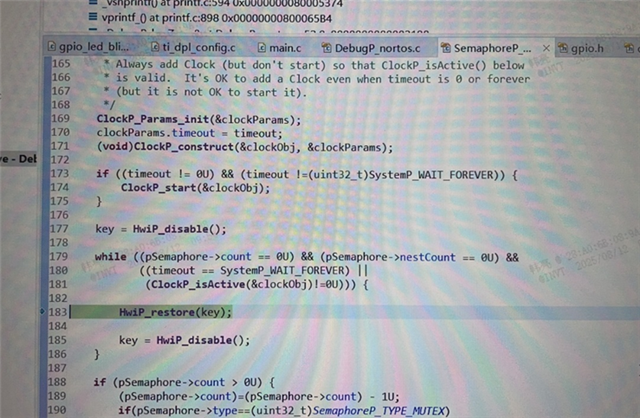

Warm boot causes DebugP_log() to hang. A53 stucks in the while loop in SemaphoreP_pend().

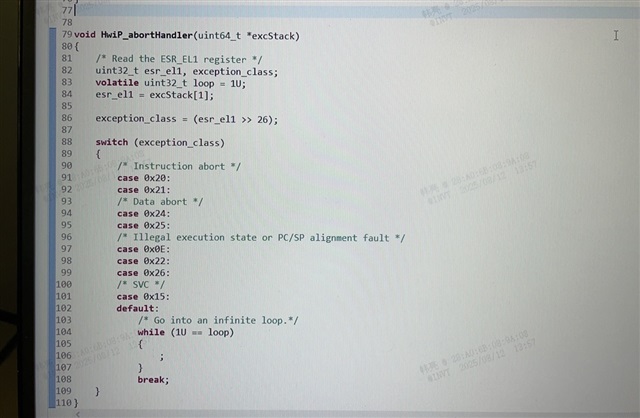

If DebugP_log() is commented out, it causes ClockP_sleep() to hang. A53 stucks in the while loop in HwiP_abortHandler().

ESR_EL1=0x02000000, ELR_EL1 =0x80001180

If cold boot, or both DebugP_log() and ClockP_sleep() are commented, system runs normally.

- Affected Cores:

Cortex-A53only. R5F cores operate normally during identical warm boot sequences. - Repro Steps:

- Cold boot → System runs normally.

- Trigger warm boot (watchdog reset/IPC command).

- A53 fails at first

HVCcall post-reset

I consulted this issue with deepseek (an AI tool similar to Chat-GPT), and here is the response from the AI.

2. Problem(Answer from AI)

The HVC (Hypervisor Call) instruction executes successfully during cold boot but throws an illegal exception during warm boot when:

- Core is stuck in EL1 (incorrect Exception Level).

- Hypervisor context (e.g.,

HCR_EL2,VTTBR_EL2) is not restored. - TI-SYSFW services are in an invalid state for HVC handling.

3. Root Cause Analysis(Answer from AI)

A. Core Architectural Differences

| Cortex-A53 | Cortex-R5F |

|---|---|

Supports EL2 + HVC |

No EL2/HVC support |

| Light reset: Preserves EL state | Full reset: Clears all state |

B. AM64x-Specific Behavior

- Warm Boot on A53:

- Only partial reset (peripherals reinitialized, but core registers/EL state preserved).

- Post-reset, A53 resumes at

EL1→HVCrequiresEL2→ Illegal Execution State (ESR 0x02000000).

- Why R5F Works:

R5F cores undergo full reset → Boot from scratch → No EL state conflicts.

C. SYSFW Interaction

- HVC calls rely on pre-initialized Hypervisor services that become invalid post-warm boot.

- R5F uses IPC (not HVC) to communicate with SYSFW, avoiding this dependency.

4. Recommended Solutions(Answer from AI)

Option 1: Skip HVC During Warm Boot (Least Intrusive)

Option 2: Force EL2 Transition During Warm Boot

Key Request to TI

- Clarify Expected Warm Boot Behavior:

- Should TI-SYSFW auto-reinitialize HVC services post-warm reset?

- Official Guidance:

- Is Option 1 (skipping HVC) endorsed for production?

- Errata Documentation:

- Is this a known silicon issue?

- Is there an official fix method?