Other Parts Discussed in Thread: TDA4VH

Tool/software:

Hi.

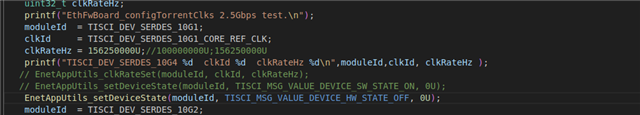

The sgmii phy of 2-0 is debugged in rtos.

TDA4VH SDK0902 cpsw port4 serdes1 lane1<-----sgmii----->switch.

{ /* "P3" */

.macPort = ENET_MAC_PORT_4,

.mii = { ENET_MAC_LAYER_GMII, ENET_MAC_SUBLAYER_SERIAL }, /*ENET_MAC_SUBLAYER_SERIAL SGMII*/

.phyCfg =

{

.phyAddr = ENETPHY_INVALID_PHYADDR,

.isStrapped = BFALSE,

.skipExtendedCfg = BFALSE,

.extendedCfg = NULL,

.extendedCfgSize = 0U,

},

.sgmiiMode = ENET_MAC_SGMIIMODE_SGMII_FORCEDLINK,

.linkCfg = { ENET_SPEED_1GBIT, ENET_DUPLEX_FULL },

},

Board_STATUS Board_CfgSgmii_serdes1(void)

{

CSL_SerdesResult result;

CSL_SerdesLaneEnableStatus laneRetVal = CSL_SERDES_LANE_ENABLE_NO_ERR;

CSL_SerdesLaneEnableParams serdesLane0EnableParams = {0};

memset(&serdesLane0EnableParams, 0, sizeof(serdesLane0EnableParams));

/* SGMII Config */

serdesLane0EnableParams.serdesInstance = (CSL_SerdesInstance)CSL_TORRENT_SERDES1;

serdesLane0EnableParams.baseAddr = CSL_WIZ16B8M4CT3_1_WIZ16B8M4CT3_BASE;

serdesLane0EnableParams.refClock = CSL_SERDES_REF_CLOCK_100M;

serdesLane0EnableParams.refClkSrc = CSL_SERDES_REF_CLOCK_INT0;

serdesLane0EnableParams.linkRate = CSL_SERDES_LINK_RATE_1p25G;

serdesLane0EnableParams.numLanes = 0x1;

serdesLane0EnableParams.laneMask = 0x2;

serdesLane0EnableParams.SSC_mode = CSL_SERDES_NO_SSC;

serdesLane0EnableParams.phyType = CSL_SERDES_PHY_TYPE_SGMII;

serdesLane0EnableParams.operatingMode = CSL_SERDES_FUNCTIONAL_MODE;

serdesLane0EnableParams.phyInstanceNum = 0;//BOARD_SERDES_LANE_SELECT_CPSW;

serdesLane0EnableParams.pcieGenType = CSL_SERDES_PCIE_GEN3;

serdesLane0EnableParams.laneCtrlRate[0] = CSL_SERDES_LANE_FULL_RATE;

serdesLane0EnableParams.loopbackMode[0] = CSL_SERDES_LOOPBACK_DISABLED;

serdesLane0EnableParams.laneCtrlRate[1] = CSL_SERDES_LANE_FULL_RATE;

serdesLane0EnableParams.loopbackMode[1] = CSL_SERDES_LOOPBACK_DISABLED;

CSL_serdesPorReset(serdesLane0EnableParams.baseAddr);

/* Select the IP type, IP instance num, Serdes Lane Number */

CSL_serdesIPSelect(CSL_CTRL_MMR0_CFG0_BASE,

serdesLane0EnableParams.phyType,

serdesLane0EnableParams.phyInstanceNum,

serdesLane0EnableParams.serdesInstance,

1U);

result = CSL_serdesRefclkSel(CSL_CTRL_MMR0_CFG0_BASE,

serdesLane0EnableParams.baseAddr,

serdesLane0EnableParams.refClock,

serdesLane0EnableParams.refClkSrc,

serdesLane0EnableParams.serdesInstance,

serdesLane0EnableParams.phyType);

if (result != CSL_SERDES_NO_ERR)

{

return BOARD_FAIL;

}

/* Assert PHY reset and disable all lanes */

CSL_serdesDisablePllAndLanes(serdesLane0EnableParams.baseAddr, serdesLane0EnableParams.numLanes, serdesLane0EnableParams.laneMask);

/* Load the Serdes Config File */

result = CSL_serdesEthernetInit(&serdesLane0EnableParams);

/* Return error if input params are invalid */

if (result != CSL_SERDES_NO_ERR)

{

return BOARD_FAIL;

}

/* Common Lane Enable API for lane enable, pll enable etc */

laneRetVal = CSL_serdesLaneEnable(&serdesLane0EnableParams);

if (laneRetVal != 0)

{

return BOARD_FAIL;

}

return BOARD_SOK;

}

Now devmem2 0x0c000414 is 0x00000030

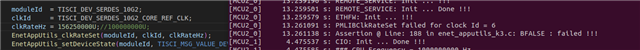

How should I troubleshoot a "Link up" failure issue?

Thanks and regards,

jun