Tool/software:

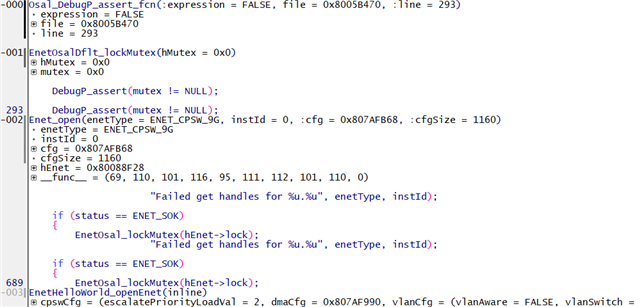

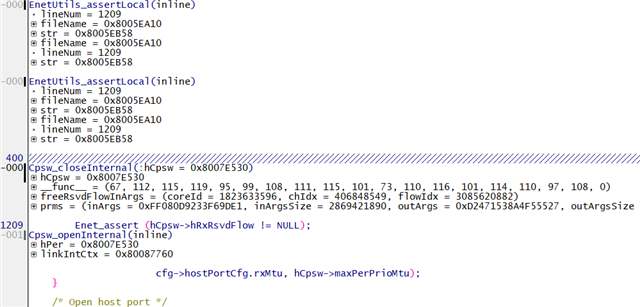

We are working on custom bootloader using TI drivers. We initialize the SBL first with following macros and then the MPU where UART and MMC drivers are working. But the enet helloworld example is not working. What are the changes required for it work in MPU? we want tftp to work with LWIP on top of Enet LLD.