Other Parts Discussed in Thread: TDA4VL

Tool/software:

SDK info: v805

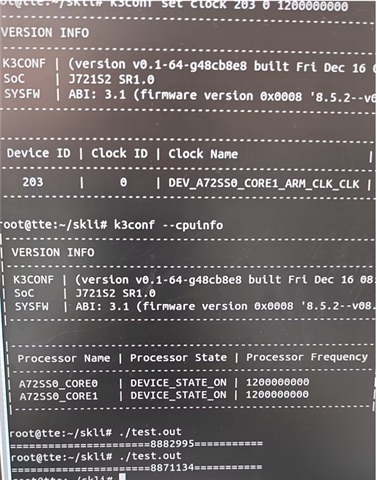

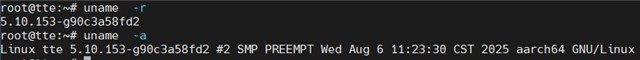

The motherboard tda4vmeco A72 core is configured with a clock speed of 2.0GHz and set to a clock speed of 1.2GHz. When running the same code (basic pure CPU calculations), the clock speed of 1.2GHz is actually slower than that of 2.0GHz.

Here is our test code:

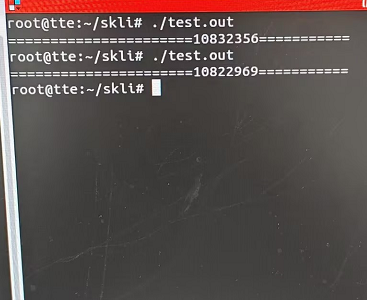

Except for the different clock frequency settings, everything else is in the same environment (CPU load idle). As shown in the above code: the operation time from 0 to 100000000 is about 104ms at 2.0GHZ and about 88ms at 1.2GHZ.

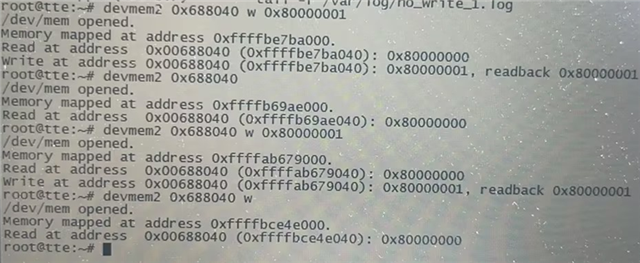

Using functions such as appLogGetGlobalTimeInUsec, getSysClockTimeMsec, and getSysTimeUsec to calculate time consumption results is the same, and the results of binding CPU cores to run programs are also consistent.

so why?