Other Parts Discussed in Thread: AM625

Tool/software:

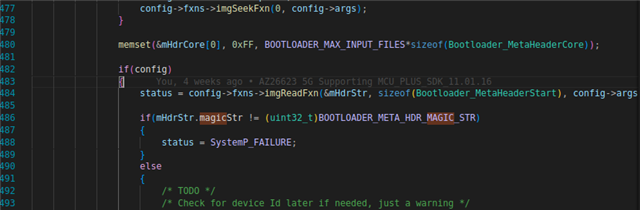

I have seen a weird behavior where my spl is working with its lpddr configuration but it is failing when I use the same for sbl why does this happen .If i do put logs and check it fails here differently at here ...

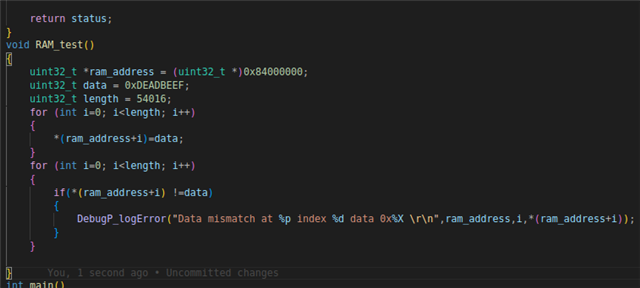

Then i proceeded to do some ram test where i do some write and read similarly like 0xDEADBEEF to offsets and read it back it fails can you explain me why this might be happening ?

SYSFW Firmware Version 11.1.2--v11.01.02 (Fancy Rat)

SYSFW Firmware revision 0xb

SYSFW ABI revision 4.0

Performing ram test

ERROR: RAM_test:275: Data mismatch at 84000000 index 0 data 0x0

ERROR: RAM_test:275: Data mismatch at 84000004 index 1 data 0x0

ERROR: RAM_test:275: Data mismatch at 84000008 index 2 data 0xBE000000

ERROR: RAM_test:275: Data mismatch at 8400000C index 3 data 0xFEEFFEEF

ERROR: RAM_test:275: Data mismatch at 84000010 index 4 data 0xFE00FE00

ERROR: RAM_test:275: Data mismatch at 84000014 index 5 data 0xFE00FE00

ERROR: RAM_test:275: Data mismatch at 84000018 index 6 data 0xFEEFFEEF

ERROR: RAM_test:275: Data mismatch at 8400001C index 7 data 0xFE00FE00

ERROR: RAM_test:275: Data mismatch at 84000020 index 8 data 0x0

ERROR: RAM_test:275: Data mismatch at 84000024 index 9 data 0x0

ERROR: RAM_test:275: Data mismatch at 84000028 index 10 data 0xBE000000

ERROR: RAM_test:275: Data mismatch at 8400002C index 11 data 0xFEEFFEEF

ERROR: RAM_test:275: Data mismatch at 84000030 index 12 data 0xFE00FE00

ERROR: RAM_test:275: Data mismatch at 84000034 index 13 data 0xFEEFFEEF

ERROR: RAM_test:275: Data mismatch at 84000038 index 14 data 0xFEEFFEEF

ERROR: RAM_test:275: Data mismatch at 8400003C index 15 data 0xFEEFFEFF

ERROR: RAM_test:275: Data mismatch at 84000040 index 16 data 0x0

ERROR: RAM_test:275: Data mismatch at 84000044 index 17 data 0xDEADDEAC

ERROR: RAM_test:275: Data mismatch at 84000048 index 18 data 0xBEEF0000

ERROR: RAM_test:275: Data mismatch at 8400004C index 19 data 0xFEEFFEEF

ERROR: RAM_test:275: Data mismatch at 84000050 index 20 data 0xFEEFFEEF

ERROR: RAM_test:275: Data mismatch at 84000054 index 21 data 0xFEEFFEEF

ERROR: RAM_test:275: Data mismatch at 84000058 index 22 data 0xFEEFFEEF

ERROR: RAM_test:275: Data mismatch at 8400005C index 23 data 0xFEEFFEEF

ERROR: RAM_test:275: Data mismatch at 84000060 index 24 data 0x0

ERROR: RAM_test:275: Data mismatch at 84000064 index 25 data 0xBEEF0000

ERROR: RAM_test:275: Data mismatch at 84000068 index 26 data 0xFEEFFEEF

ERROR: RAM_test:275: Data mismatch at 8400006C index 27 data 0xFEEFFEEF

ERROR: RAM_test:275: Data mismatch at 84000070 index 28 data 0xFEEFFEEF

ERROR: RAM_test:275: Data mismatch at 84000074 index 29 data 0xFEEFFEEF

ERROR: RAM_test:275: Data mismatch at 84000078 index 30 data 0xFEEFFEEF

ERROR: RAM_test:275: Data mismatch at 8400007C index 31 data 0xFEEFFEEF

ERROR: RAM_test:275: Data mismatch at 84000080 index 32 data 0x0

ERROR: RAM_test:275: Data mismatch at 84000084 index 33 data 0xDEADDEAC

ERROR: RAM_test:275: Data mismatch at 84000088 index 34 data 0xBEEF0000

ERROR: RAM_test:275: Data mismatch at 8400008C index 35 data 0xFEEFFEEF

ERROR: RAM_test:275: Data mismatch at 84000090 index 36 data 0xFEEFFEEF

ERROR: RAM_test:275: Data mismatch at 84000094 index 37 data 0xFEEFFEEF

ERROR: RAM_test:275: Data mismatch at 84000098 index 38 data 0xFEEFFEEF

ERROR: RAM_test:275: Data mismatch at 8400009C index 39 data 0xFEEFFEEF

ERROR: RAM_test:275: Data mismatch at 840000A0 index 40 data 0x0

ERROR: RAM_test:275: Data mismatch at 840000A4 index 41 data 0x0

ERROR: RAM_test:275: Data mismatch at 840000A8 index 42 data 0xBEEF0000

ERROR: RAM_test:275: Data mismatch at 840000AC index 43 data 0xFEEFFEEF

ERROR: RAM_test:275: Data mismatch at 840000B0 index 44 data 0xFEEFFEEF