Tool/software:

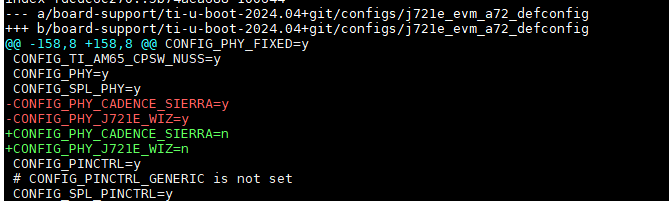

hi:

Using TDA4's CPSW9G, connecting to phy chip, link up successfully but we can't ping other devices

SDK-10.01

1. uboot

2.linux dts k3-j721e-common-proc-board.dts

&usb_serdes_mux {

idle-states = <1>, <0>; /* USB0 to SERDES3, USB1 to SERDES1 */

};

/*

&serdes_ln_ctrl {

idle-states = <J721E_SERDES0_LANE0_PCIE0_LANE0>, <J721E_SERDES0_LANE1_PCIE0_LANE1>,

<J721E_SERDES1_LANE0_PCIE1_LANE0>, <J721E_SERDES1_LANE1_PCIE1_LANE1>,

<J721E_SERDES2_LANE0_PCIE2_LANE0>, <J721E_SERDES2_LANE1_PCIE2_LANE1>,

<J721E_SERDES3_LANE0_USB3_0_SWAP>, <J721E_SERDES3_LANE1_USB3_0>,

<J721E_SERDES4_LANE0_EDP_LANE0>, <J721E_SERDES4_LANE1_EDP_LANE1>,

<J721E_SERDES4_LANE2_EDP_LANE2>, <J721E_SERDES4_LANE3_EDP_LANE3>;

};

*/

&serdes_ln_ctrl {

idle-states = //<J721E_SERDES0_LANE0_QSGMII_LANE1>, <J721E_SERDES0_LANE1_QSGMII_LANE2>,

<J721E_SERDES0_LANE0_PCIE0_LANE0>, <J721E_SERDES0_LANE1_QSGMII_LANE2>,

<J721E_SERDES1_LANE0_USB3_1_SWAP>, <J721E_SERDES1_LANE1_USB3_1>,

<J721E_SERDES2_LANE0_PCIE2_LANE0>, <J721E_SERDES2_LANE1_PCIE2_LANE1>,

<J721E_SERDES3_LANE0_IP1_UNUSED>, <J721E_SERDES3_LANE1_USB3_0>,

<J721E_SERDES4_LANE0_QSGMII_LANE5>, <J721E_SERDES4_LANE1_QSGMII_LANE6>,

<J721E_SERDES4_LANE2_QSGMII_LANE7>, <J721E_SERDES4_LANE3_QSGMII_LANE8>;

};

&serdes_wiz3 {

typec-dir-gpios = <&main_gpio1 3 GPIO_ACTIVE_HIGH>;

typec-dir-debounce-ms = <700>; /* TUSB321, tCCB_DEFAULT 133 ms */

};

&serdes3 {

serdes3_usb_link: phy@0 {

reg = <0>;

cdns,num-lanes = <2>;

#phy-cells = <0>;

cdns,phy-type = <PHY_TYPE_USB3>;

resets = <&serdes_wiz3 1>, <&serdes_wiz3 2>;

};

};

&usbss0 {

pinctrl-names = "default";

pinctrl-0 = <&main_usbss0_pins_default>;

ti,vbus-divider;

};

&usb0 {

dr_mode = "otg";

maximum-speed = "super-speed";

phys = <&serdes3_usb_link>;

phy-names = "cdns3,usb3-phy";

};

&usbss1 {

pinctrl-names = "default";

pinctrl-0 = <&main_usbss1_pins_default>;

ti,usb2-only;

};

&usb1 {

dr_mode = "host";

maximum-speed = "high-speed";

};

&ospi1 {

pinctrl-names = "default";

pinctrl-0 = <&mcu_fss0_ospi1_pins_default>;

flash@0 {

compatible = "jedec,spi-nor";

reg = <0x0>;

spi-tx-bus-width = <1>;

spi-rx-bus-width = <4>;

spi-max-frequency = <40000000>;

cdns,tshsl-ns = <60>;

cdns,tsd2d-ns = <60>;

cdns,tchsh-ns = <60>;

cdns,tslch-ns = <60>;

cdns,read-delay = <2>;

partitions {

compatible = "fixed-partitions";

#address-cells = <1>;

#size-cells = <1>;

partition@0 {

label = "qspi.tiboot3";

reg = <0x0 0x80000>;

};

partition@80000 {

label = "qspi.tispl";

reg = <0x80000 0x200000>;

};

partition@280000 {

label = "qspi.u-boot";

reg = <0x280000 0x400000>;

};

partition@680000 {

label = "qspi.env";

reg = <0x680000 0x20000>;

};

partition@6a0000 {

label = "qspi.env.backup";

reg = <0x6a0000 0x20000>;

};

partition@6c0000 {

label = "qspi.sysfw";

reg = <0x6c0000 0x100000>;

};

partition@800000 {

label = "qspi.rootfs";

reg = <0x800000 0x37c0000>;

};

partition@3fe0000 {

label = "qspi.phypattern";

reg = <0x3fe0000 0x20000>;

};

};

};

};

&tscadc0 {

status = "okay";

adc {

ti,adc-channels = <0 1 2 3 4 5 6 7>;

};

};

&tscadc1 {

status = "okay";

adc {

ti,adc-channels = <0 1 2 3 4 5 6 7>;

};

};

&main_i2c0 {

status = "okay";

pinctrl-names = "default";

pinctrl-0 = <&main_i2c0_pins_default>;

clock-frequency = <400000>;

exp1: gpio@20 {

compatible = "ti,tca6416";

reg = <0x20>;

gpio-controller;

#gpio-cells = <2>;

};

exp2: gpio@22 {

compatible = "ti,tca6424";

reg = <0x22>;

gpio-controller;

#gpio-cells = <2>;

p09-hog {

/* P11 - MCASP/TRACE_MUX_S0 */

gpio-hog;

gpios = <9 GPIO_ACTIVE_HIGH>;

output-low;

line-name = "MCASP/TRACE_MUX_S0";

};

p10-hog {

/* P12 - MCASP/TRACE_MUX_S1 */

gpio-hog;

gpios = <10 GPIO_ACTIVE_HIGH>;

output-high;

line-name = "MCASP/TRACE_MUX_S1";

};

};

};

&main_i2c1 {

status = "okay";

pinctrl-names = "default";

pinctrl-0 = <&main_i2c1_pins_default>;

clock-frequency = <400000>;

exp4: gpio@20 {

compatible = "ti,tca6408";

reg = <0x20>;

gpio-controller;

#gpio-cells = <2>;

pinctrl-names = "default";

pinctrl-0 = <&main_i2c1_exp4_pins_default>;

interrupt-parent = <&main_gpio1>;

interrupts = <11 IRQ_TYPE_EDGE_FALLING>;

interrupt-controller;

#interrupt-cells = <2>;

};

};

//&k3_clks {

// /* Confiure AUDIO_EXT_REFCLK2 pin as output */

// pinctrl-names = "default";

// pinctrl-0 = <&audi_ext_refclk2_pins_default>;

//};

&main_i2c3 {

status = "okay";

pinctrl-names = "default";

pinctrl-0 = <&main_i2c3_pins_default>;

clock-frequency = <400000>;

exp3: gpio@20 {

compatible = "ti,tca6408";

reg = <0x20>;

gpio-controller;

#gpio-cells = <2>;

};

pcm3168a_1: audio-codec@44 {

compatible = "ti,pcm3168a";

reg = <0x44>;

#sound-dai-cells = <1>;

reset-gpios = <&exp3 0 GPIO_ACTIVE_LOW>;

/* C_AUDIO_REFCLK2 -> RGMII6_RXC (W26) */

clocks = <&k3_clks 157 371>;

clock-names = "scki";

/* HSDIV3_16FFT_MAIN_4_HSDIVOUT2_CLK -> REFCLK2 */

assigned-clocks = <&k3_clks 157 371>;

assigned-clock-parents = <&k3_clks 157 400>;

assigned-clock-rates = <24576000>; /* for 48KHz */

VDD1-supply = <&vsys_3v3>;

VDD2-supply = <&vsys_3v3>;

VCCAD1-supply = <&vsys_5v0>;

VCCAD2-supply = <&vsys_5v0>;

VCCDA1-supply = <&vsys_5v0>;

VCCDA2-supply = <&vsys_5v0>;

};

};

&main_i2c6 {

status = "okay";

pinctrl-names = "default";

pinctrl-0 = <&main_i2c6_pins_default>;

clock-frequency = <400000>;

exp5: gpio@20 {

compatible = "ti,tca6408";

reg = <0x20>;

gpio-controller;

#gpio-cells = <2>;

};

};

&mcu_cpsw {

pinctrl-names = "default";

pinctrl-0 = <&mcu_cpsw_pins_default>, <&mcu_mdio_pins_default>;

cpts@3d000 {

/* Map HW4_TS_PUSH to GENF1 */

ti,pps = <3 1>;

};

};

&davinci_mdio {

phy0: ethernet-phy@0 {

reg = <0>;

ti,rx-internal-delay = <DP83867_RGMIIDCTL_2_00_NS>;

ti,fifo-depth = <DP83867_PHYCR_FIFO_DEPTH_4_B_NIB>;

};

};

&cpsw_port1 {

phy-mode = "rgmii-rxid";

phy-handle = <&phy0>;

};

//&dss {

// /*

// * These clock assignments are chosen to enable the following outputs:

// *

// * VP0 - DisplayPort SST

// * VP1 - DPI0

// * VP2 - DSI

// * VP3 - DPI1

// */

//

// assigned-clocks = <&k3_clks 152 1>,

// <&k3_clks 152 4>,

// <&k3_clks 152 9>,

// <&k3_clks 152 13>;

// assigned-clock-parents = <&k3_clks 152 2>, /* PLL16_HSDIV0 */

// <&k3_clks 152 6>, /* PLL19_HSDIV0 */

// <&k3_clks 152 11>, /* PLL18_HSDIV0 */

// <&k3_clks 152 18>; /* PLL23_HSDIV0 */

//};

//

//&dss_ports {

// port {

// dpi0_out: endpoint {

// remote-endpoint = <&dp0_in>;

// };

// };

//};

//

//&dp0_ports {

// #address-cells = <1>;

// #size-cells = <0>;

//

// port@0 {

// reg = <0>;

// dp0_in: endpoint {

// remote-endpoint = <&dpi0_out>;

// };

// };

//

// port@4 {

// reg = <4>;

// dp0_out: endpoint {

// remote-endpoint = <&dp_connector_in>;

// };

// };

//};

//

//&mcasp10 {

// status = "okay";

// #sound-dai-cells = <0>;

//

// pinctrl-names = "default";

// pinctrl-0 = <&mcasp10_pins_default>;

//

// op-mode = <0>; /* MCASP_IIS_MODE */

// tdm-slots = <2>;

// auxclk-fs-ratio = <256>;

//

// serial-dir = < /* 0: INACTIVE, 1: TX, 2: RX */

// 1 1 1 1

// 2 2 2 0

// >;

// tx-num-evt = <0>;

// rx-num-evt = <0>;

//};

//

&cpsw0 {

status = "okay";

pinctrl-names = "default";

pinctrl-0 = <&rgmii3_default_pins>;

};

&cpsw0_port1 {

status = "disabled";

};

&cpsw0_port2 {

status = "okay";

phy-handle = <&cpsw9g_phy4>;

phy-mode = "sgmii";

mac-address = [00 00 00 00 00 00];

phys = <&cpsw0_phy_gmii_sel 2>,<&serdes0_sgmii_link>;

phy-names = "portmode", "serdes-phy";

};

&cpsw0_port3 {

status = "okay";

phy-handle = <&cpsw9g_phy13>;

phy-mode = "rgmii-rxid";

mac-address = [00 00 00 00 00 00];

phys = <&cpsw0_phy_gmii_sel 3>;

};

&cpsw0_port4 {

status = "disabled";

};

&cpsw0_port5 {

status = "okay";

phy-handle = <&cpsw9g_phy0>;

phy-mode = "sgmii";

mac-address = [00 00 00 00 00 00];

phys = <&cpsw0_phy_gmii_sel 5>,<&serdes4_sgmii_link>;

phy-names = "portmode", "serdes-phy";

};

&cpsw0_port6 {

status = "okay";

phy-handle = <&cpsw9g_phy1>;

phy-mode = "sgmii";

mac-address = [00 00 00 00 00 00];

phys = <&cpsw0_phy_gmii_sel 6>;

phy-names = "portmode", "serdes-phy";

};

&cpsw0_port7 {

status = "okay";

phy-handle = <&cpsw9g_phy2>;

phy-mode = "sgmii";

mac-address = [00 00 00 00 00 00];

phys = <&cpsw0_phy_gmii_sel 7>;

phy-names = "portmode", "serdes-phy";

};

&cpsw0_port8 {

status = "okay";

phy-handle = <&cpsw9g_phy3>;

phy-mode = "sgmii";

mac-address = [00 00 00 00 00 00];

phys = <&cpsw0_phy_gmii_sel 8>;

phy-names = "portmode", "serdes-phy";

};

&cpsw9g_mdio {

status = "okay";

pinctrl-names = "default";

pinctrl-0 = <&mdio0_pins_default>;

//reset-gpios = <&exp2 17 GPIO_ACTIVE_LOW>;

reset-post-delay-us = <120000>;

//bus_freq = <1000000>;

#address-cells = <1>;

#size-cells = <0>;

cpsw9g_phy0: ethernet-phy@4 {

reg = <4>;

};

cpsw9g_phy1: ethernet-phy@5 {

reg = <5>;

};

cpsw9g_phy2: ethernet-phy@8 {

reg = <8>;

};

cpsw9g_phy3: ethernet-phy@10 {

reg = <10>;

};

cpsw9g_phy4: ethernet-phy@12 {

reg = <12>;

};

cpsw9g_phy13: ethernet-phy@13 {

reg = <13>;

ti,rx-internal-delay = <DP83867_RGMIIDCTL_2_00_NS>;

ti,fifo-depth = <DP83867_PHYCR_FIFO_DEPTH_4_B_NIB>;

};

};

&main_pmx0 {

mdio0_pins_default: mdio0-default-pins {

pinctrl-single,pins = <

J721E_IOPAD(0x1bc, PIN_OUTPUT, 0) /* (V24) MDIO0_MDC */

J721E_IOPAD(0x1b8, PIN_INPUT, 0) /* (V26) MDIO0_MDIO */

>;

};

};

&serdes_wiz0 {

status = "okay";

};

&wiz0_pll1_refclk {

assigned-clocks = <&wiz0_pll1_refclk>;

assigned-clock-parents = <&k3_clks 292 0>;

};

&serdes_wiz1 {

status = "disabled";

};

&serdes_wiz2 {

status = "disabled";

};

&serdes0 {

status = "okay";

assigned-clocks = <&serdes0 CDNS_SIERRA_PLL_CMNLC>, <&serdes0 CDNS_SIERRA_PLL_CMNLC1>;

assigned-clock-parents = <&wiz0_pll1_refclk>, <&wiz0_pll1_refclk>;

//assigned-clocks = <&serdes0 CDNS_SIERRA_PLL_CMNLC1>;

//assigned-clock-parents = <&wiz0_pll1_refclk>;

#address-cells = <1>;

#size-cells = <0>;

/*

serdes0_pcie_link: phy@0 {

reg = <0>;

cdns,num-lanes = <1>;

#phy-cells = <0>;

cdns,phy-type = <PHY_TYPE_PCIE>;

resets = <&serdes_wiz0 1>;

};

*/

serdes0_sgmii_link: phy@0 {

reg = <0>;

cdns,num-lanes = <2>;

#phy-cells = <0>;

cdns,phy-type = <PHY_TYPE_SGMII>;

resets = <&serdes_wiz0 1>,<&serdes_wiz0 2>;

};

};

&serdes_wiz4 {

status = "okay";

};

&wiz4_pll0_refclk {

assigned-clocks = <&wiz0_pll0_refclk>;

assigned-clock-parents = <&k3_clks 297 9>;

};

&serdes4 {

assigned-clocks = <&serdes4 CDNS_SIERRA_PLL_CMNLC1>;

assigned-clock-parents = <&wiz4_pll0_refclk>;

#address-cells = <1>;

#size-cells = <0>;

status = "okay";

serdes4_sgmii_link: phy@0 {

reg = <0>;

cdns,num-lanes = <4>;

#phy-cells = <0>;

cdns,phy-type = <PHY_TYPE_SGMII>;

resets = <&serdes_wiz4 1>, <&serdes_wiz4 2>, <&serdes_wiz4 3>, <&serdes_wiz4 4>;

};

};

/*

&cmn_refclk1 {

clock-frequency = <100000000>;

};

&wiz0_pll1_refclk {

assigned-clocks = <&wiz0_pll1_refclk>;

assigned-clock-parents = <&cmn_refclk1>;

};

&wiz0_refclk_dig {

assigned-clocks = <&wiz0_refclk_dig>;

assigned-clock-parents = <&cmn_refclk1>;

};

&wiz1_pll1_refclk {

assigned-clocks = <&wiz1_pll1_refclk>;

assigned-clock-parents = <&cmn_refclk1>;

};

&wiz1_refclk_dig {

assigned-clocks = <&wiz1_refclk_dig>;

assigned-clock-parents = <&cmn_refclk1>;

};

&wiz2_pll1_refclk {

assigned-clocks = <&wiz2_pll1_refclk>;

assigned-clock-parents = <&cmn_refclk1>;

};

&wiz2_refclk_dig {

assigned-clocks = <&wiz2_refclk_dig>;

assigned-clock-parents = <&cmn_refclk1>;

};

&serdes0 {

assigned-clocks = <&serdes0 CDNS_SIERRA_PLL_CMNLC>;

assigned-clock-parents = <&wiz0_pll1_refclk>;

serdes0_pcie_link: phy@0 {

reg = <0>;

cdns,num-lanes = <1>;

#phy-cells = <0>;

cdns,phy-type = <PHY_TYPE_PCIE>;

resets = <&serdes_wiz0 1>;

};

};

*/

&serdes1 {

assigned-clocks = <&serdes1 CDNS_SIERRA_PLL_CMNLC>;

assigned-clock-parents = <&wiz1_pll1_refclk>;

status = "disabled"; //kfl

serdes1_pcie_link: phy@0 {

reg = <0>;

cdns,num-lanes = <2>;

#phy-cells = <0>;

cdns,phy-type = <PHY_TYPE_PCIE>;

resets = <&serdes_wiz1 1>, <&serdes_wiz1 2>;

};

};

&serdes2 {

assigned-clocks = <&serdes2 CDNS_SIERRA_PLL_CMNLC>;

assigned-clock-parents = <&wiz2_pll0_refclk>;

status = "disabled"; //kfl

serdes2_pcie_link: phy@0 {

reg = <0>;

cdns,num-lanes = <2>;

#phy-cells = <0>;

cdns,phy-type = <PHY_TYPE_PCIE>;

resets = <&serdes_wiz2 1>, <&serdes_wiz2 2>;

};

};

/*

&serdes4 {

torrent_phy_dp: phy@0 {

reg = <0>;

resets = <&serdes_wiz4 1>;

cdns,phy-type = <PHY_TYPE_DP>;

cdns,num-lanes = <4>;

cdns,max-bit-rate = <2700>;

#phy-cells = <0>;

};

};

&mhdp {

phys = <&torrent_phy_dp>;

phy-names = "dpphy";

pinctrl-names = "default";

pinctrl-0 = <&dp0_pins_default>;

};

&pcie0_rc {

status = "okay";

reset-gpios = <&exp1 6 GPIO_ACTIVE_HIGH>;

phys = <&serdes0_pcie_link>;

phy-names = "pcie-phy";

num-lanes = <1>;

};

&pcie1_rc {

status = "okay";

reset-gpios = <&exp1 2 GPIO_ACTIVE_HIGH>;

phys = <&serdes1_pcie_link>;

phy-names = "pcie-phy";

num-lanes = <2>;

};

&pcie2_rc {

status = "okay";

reset-gpios = <&exp2 20 GPIO_ACTIVE_HIGH>;

phys = <&serdes2_pcie_link>;

phy-names = "pcie-phy";

num-lanes = <2>;

};

*/

3. k3-j721e-main.dtsi

serdes_wiz4: wiz@5050000 {

//compatible = "ti,am64-wiz-10g";

compatible = "ti,j721e-wiz-10g";

#address-cells = <1>;

#size-cells = <1>;

power-domains = <&k3_pds 297 TI_SCI_PD_EXCLUSIVE>;

clocks = <&k3_clks 297 1>, <&k3_clks 297 9>, <&cmn_refclk>;

clock-names = "fck", "core_ref_clk", "ext_ref_clk";

assigned-clocks = <&k3_clks 297 9>;

assigned-clock-parents = <&k3_clks 297 13>;//10

//assigned-clock-rates = <19200000>;

num-lanes = <4>;

#reset-cells = <1>;

#clock-cells = <1>;

ranges = <0x05050000 0x00 0x05050000 0x010000>,

<0x0a030a00 0x00 0x0a030a00 0x40>;

wiz4_pll0_refclk: pll0-refclk {

clocks = <&k3_clks 297 9>, <&cmn_refclk>;

clock-output-names = "wiz4_pll0_refclk";

#clock-cells = <0>;

assigned-clocks = <&wiz4_pll0_refclk>;

assigned-clock-parents = <&k3_clks 297 9>;

};

wiz4_pll1_refclk: pll1-refclk {

clocks = <&k3_clks 297 9>, <&cmn_refclk>;

clock-output-names = "wiz4_pll1_refclk";

#clock-cells = <0>;

assigned-clocks = <&wiz4_pll1_refclk>;

assigned-clock-parents = <&k3_clks 297 9>;

};

wiz4_refclk_dig: refclk-dig {

clocks = <&k3_clks 297 9>, <&cmn_refclk>;

clock-output-names = "wiz4_refclk_dig";

#clock-cells = <0>;

assigned-clocks = <&wiz4_refclk_dig>;

assigned-clock-parents = <&k3_clks 297 9>;

};

wiz4_cmn_refclk_dig_div: cmn-refclk-dig-div {

clocks = <&wiz4_refclk_dig>;

#clock-cells = <0>;

};

wiz4_cmn_refclk1_dig_div: cmn-refclk1-dig-div {

clocks = <&wiz4_pll1_refclk>;

#clock-cells = <0>;

};

serdes4: serdes@5050000 {

/*

* Note: we also map DPTX PHY registers as the Torrent

* needs to manage those.

*/

compatible = "ti,j721e-serdes-10g";

reg = <0x05050000 0x010000>,

<0x0a030a00 0x40>; /* DPTX PHY */

reg-names = "torrent_phy", "dptx_phy";

resets = <&serdes_wiz4 0>;

reset-names = "torrent_reset";

// clocks = <&serdes_wiz4 TI_WIZ_PLL0_REFCLK>;

clocks = <&wiz4_pll0_refclk>; //pll1

clock-names = "refclk";

/* assigned-clocks = <&serdes_wiz4 TI_WIZ_PLL0_REFCLK>,

<&serdes_wiz4 TI_WIZ_PLL1_REFCLK>,

<&serdes_wiz4 TI_WIZ_REFCLK_DIG>;

assigned-clock-parents = <&k3_clks 297 9>,

<&k3_clks 297 9>,

<&k3_clks 297 9>;

*/

#address-cells = <1>;

#size-cells = <0>;

};

};

4.remove j7-main-r5f0_0-fw

5. remove uenv.txt overlays

6. ethtool eth show link

root@j721e-evm:/home/weston/scripts# ethtool eth6

Settings for eth6:

Supported ports: [ TP MII ]

Supported link modes: 1000baseT/Full

Supported pause frame use: Symmetric

Supports auto-negotiation: No

Supported FEC modes: Not reported

Advertised link modes: Not reported

Advertised pause frame use: Symmetric

Advertised auto-negotiation: No

Advertised FEC modes: Not reported

Speed: 1000Mb/s

Duplex: Full

Auto-negotiation: off

Port: Twisted Pair

PHYAD: 10

Transceiver: external

MDI-X: Unknown

Supports Wake-on: d

Wake-on: d

Current message level: 0x000020f7 (8439)

drv probe link ifdown ifup rx_err tx_err hw

Link detected: yes

7. k3conf dump clock 297

root@j721e-evm:~# k3conf dump clock 297

|------------------------------------------------------------------------------|

| VERSION INFO |

|------------------------------------------------------------------------------|

| K3CONF | (version 0.3-nogit built Thu Jul 25 14:13:02 UTC 2024) |

| SoC | J721E SR1.1 |

| SYSFW | ABI: 4.0 (firmware version 0x000a '10.1.6--v10.01.06 (Fiery Fox))') |

|------------------------------------------------------------------------------|

|--------------------------------------------------------------------------------------------------------------------------------------|

| Device ID | Clock ID | Clock Name | Status | Clock Frequency |

|--------------------------------------------------------------------------------------------------------------------------------------|

| 297 | 0 | DEV_SERDES_10G0_IP1_LN3_TXCLK | CLK_STATE_NOT_READY | 0 |

| 297 | 1 | DEV_SERDES_10G0_CLK | CLK_STATE_READY | 125000000 |

| 297 | 2 | DEV_SERDES_10G0_IP3_LN2_TXCLK | CLK_STATE_READY | 0 |

| 297 | 3 | DEV_SERDES_10G0_IP1_LN2_TXCLK | CLK_STATE_NOT_READY | 0 |

| 297 | 4 | DEV_SERDES_10G0_IP1_LN0_TXCLK | CLK_STATE_NOT_READY | 0 |

| 297 | 5 | DEV_SERDES_10G0_IP3_LN1_TXCLK | CLK_STATE_READY | 0 |

| 297 | 6 | DEV_SERDES_10G0_IP3_LN3_TXCLK | CLK_STATE_READY | 0 |

| 297 | 7 | DEV_SERDES_10G0_IP3_LN0_TXCLK | CLK_STATE_READY | 0 |

| 297 | 8 | DEV_SERDES_10G0_IP1_LN1_TXCLK | CLK_STATE_NOT_READY | 0 |

| 297 | 9 | DEV_SERDES_10G0_CORE_REF_CLK | CLK_STATE_READY | 100000000 |

| 297 | 10 | DEV_SERDES_10G0_CORE_REF_CLK_PARENT_GLUELOGIC_HFOSC0_CLKOUT | CLK_STATE_READY | 19200000 |

| 297 | 11 | DEV_SERDES_10G0_CORE_REF_CLK_PARENT_BOARD_0_HFOSC1_CLK_OUT | CLK_STATE_READY | 0 |

| 297 | 12 | DEV_SERDES_10G0_CORE_REF_CLK_PARENT_HSDIV4_16FFT_MAIN_3_HSDIVOUT4_CLK | CLK_STATE_READY | 153846153 |

| 297 | 13 | DEV_SERDES_10G0_CORE_REF_CLK_PARENT_HSDIV4_16FFT_MAIN_2_HSDIVOUT4_CLK | CLK_STATE_READY | 100000000 |

| 297 | 14 | DEV_SERDES_10G0_IP1_LN1_REFCLK | CLK_STATE_READY | 0 |

| 297 | 15 | DEV_SERDES_10G0_IP1_LN2_RXCLK | CLK_STATE_READY | 0 |

| 297 | 16 | DEV_SERDES_10G0_IP3_LN1_TXFCLK | CLK_STATE_READY | 0 |

| 297 | 17 | DEV_SERDES_10G0_IP1_LN0_RXFCLK | CLK_STATE_READY | 0 |

| 297 | 18 | DEV_SERDES_10G0_IP1_LN3_RXCLK | CLK_STATE_READY | 0 |

| 297 | 19 | DEV_SERDES_10G0_IP3_LN3_RXCLK | CLK_STATE_READY | 0 |

| 297 | 20 | DEV_SERDES_10G0_IP3_LN1_TXMCLK | CLK_STATE_READY | 0 |

| 297 | 21 | DEV_SERDES_10G0_IP3_LN3_RXFCLK | CLK_STATE_READY | 0 |

| 297 | 22 | DEV_SERDES_10G0_IP3_LN3_REFCLK | CLK_STATE_READY | 0 |

| 297 | 23 | DEV_SERDES_10G0_IP3_LN2_RXCLK | CLK_STATE_READY | 0 |

| 297 | 24 | DEV_SERDES_10G0_IP1_LN0_TXFCLK | CLK_STATE_READY | 0 |

| 297 | 25 | DEV_SERDES_10G0_IP3_LN3_TXMCLK | CLK_STATE_READY | 0 |

| 297 | 26 | DEV_SERDES_10G0_IP3_LN1_RXFCLK | CLK_STATE_READY | 0 |

| 297 | 27 | DEV_SERDES_10G0_IP3_LN0_RXFCLK | CLK_STATE_READY | 0 |

| 297 | 28 | DEV_SERDES_10G0_IP1_LN1_TXMCLK | CLK_STATE_READY | 0 |

| 297 | 29 | DEV_SERDES_10G0_IP1_LN1_RXFCLK | CLK_STATE_READY | 0 |

| 297 | 30 | DEV_SERDES_10G0_IP3_LN3_TXFCLK | CLK_STATE_READY | 0 |

| 297 | 31 | DEV_SERDES_10G0_IP1_LN3_TXFCLK | CLK_STATE_READY | 0 |

| 297 | 32 | DEV_SERDES_10G0_IP1_LN3_TXMCLK | CLK_STATE_READY | 0 |

| 297 | 33 | DEV_SERDES_10G0_IP3_LN1_REFCLK | CLK_STATE_READY | 0 |

| 297 | 34 | DEV_SERDES_10G0_IP3_LN0_REFCLK | CLK_STATE_READY | 0 |

| 297 | 35 | DEV_SERDES_10G0_IP1_LN3_REFCLK | CLK_STATE_READY | 0 |

| 297 | 36 | DEV_SERDES_10G0_IP3_LN0_RXCLK | CLK_STATE_READY | 0 |

| 297 | 37 | DEV_SERDES_10G0_IP3_LN2_REFCLK | CLK_STATE_READY | 0 |

| 297 | 38 | DEV_SERDES_10G0_IP1_LN0_RXCLK | CLK_STATE_READY | 0 |

| 297 | 39 | DEV_SERDES_10G0_IP1_LN0_REFCLK | CLK_STATE_READY | 0 |

| 297 | 40 | DEV_SERDES_10G0_IP1_LN2_RXFCLK | CLK_STATE_READY | 0 |

| 297 | 41 | DEV_SERDES_10G0_IP1_LN1_TXFCLK | CLK_STATE_READY | 0 |

| 297 | 42 | DEV_SERDES_10G0_IP3_LN0_TXFCLK | CLK_STATE_READY | 0 |

| 297 | 43 | DEV_SERDES_10G0_REF_OUT_CLK | CLK_STATE_READY | 0 |

| 297 | 44 | DEV_SERDES_10G0_IP3_LN1_RXCLK | CLK_STATE_READY | 0 |

| 297 | 45 | DEV_SERDES_10G0_IP1_LN2_TXFCLK | CLK_STATE_READY | 0 |

| 297 | 46 | DEV_SERDES_10G0_IP1_LN0_TXMCLK | CLK_STATE_READY | 0 |

| 297 | 47 | DEV_SERDES_10G0_IP3_LN2_RXFCLK | CLK_STATE_READY | 0 |

| 297 | 48 | DEV_SERDES_10G0_IP1_LN2_TXMCLK | CLK_STATE_READY | 0 |

| 297 | 49 | DEV_SERDES_10G0_IP3_LN2_TXMCLK | CLK_STATE_READY | 0 |

| 297 | 50 | DEV_SERDES_10G0_IP1_LN2_REFCLK | CLK_STATE_READY | 0 |

| 297 | 51 | DEV_SERDES_10G0_IP3_LN2_TXFCLK | CLK_STATE_READY | 0 |

| 297 | 52 | DEV_SERDES_10G0_IP3_LN0_TXMCLK | CLK_STATE_READY | 0 |

| 297 | 53 | DEV_SERDES_10G0_IP1_LN3_RXFCLK | CLK_STATE_READY | 0 |

| 297 | 54 | DEV_SERDES_10G0_IP1_LN1_RXCLK | CLK_STATE_READY | 0 |

|--------------------------------------------------------------------------------------------------------------------------------------|

8. port5-port8 sgmii not link, and no auto negotiation no pll lock

root@j721e-evm:/home/weston/scripts# ./j7_devmem2_cpsw9g_check_status.sh

Platform: J7 TDA4VM

Command: k3conf

MDIO_ALIVE_REG (0x0c000f08) = 0x00000000

MDIO_LINK_REG (0x0c000f0c) = 0x00000000

please input your port: 1-8 5

CTRLMMR_ENET 5 CTRL (0x00104054) = 0x00000003

PORT_MODE_SEL : 3h SGMII

RGMII_ID_MODE : 0h Internal Transmit Desaly

CPSW SS RGMII 5 STATUS (0x0c000040) = 0x00000000

FULLDUPLEX : 0h Half duplex

SPEED : 0h 10Mbps

LINK : 0h Links is down

CPSW_SS_STATUS_SGMII_LINK_REG (0x0c000078) = 0x00000000

SGMII1_LINK : 0h No

CPSW_SS_SGMII_CONTROL_REG_ 5 (0x0c000510) = 0x00000000

TEST_PATTERN_EN : 0h operation

MASTER : 0h Slave Mode

LOOPBACK : 0h Not in internal loopback mode

MR_NP_LOADED : 0h --------

FAST_LINK_TIMER : 0h link timer 10ms in FIBER mode and 1.6ms in SGMII mode

MA_AN_RESTART : 0h Write 1h and tehn 0h to this bit caused the auto negotiation

MR_AN_ENABLE : 0h wirte 1 to this bit enbales the auto negotiation progess

CPSW_SS_SGMII_STATUS_REG_ 5 (0x0c000514) = 0x00000000

LOCK : 0h SEDES PLL isn't locked

MR_AN_COMPLETE : 0h no AUTO Negotiation is not complete

AN_EEROR : 0h no negotiation error

LINK : 0h link is not up

root@j721e-evm:/home/weston/scripts#

9. 0x505E000 : 0x000C0000

root@j721e-evm:/home/weston/scripts# devmem2 0x505E000

/dev/mem opened.

Memory mapped at address 0xffff8d102000.

Read at address 0x0505E000 (0xffff8d102000): 0x000C0000