Tool/software:

Hi TI,

Please help me check whether my configuration is correct.

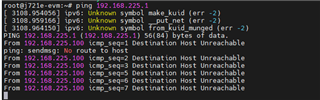

Using TDA4's CPSW9G, connecting to phy chip, link up successfully but we can't ping other devices

SDK-10.00

serdes0-lane1: rtl9010(sgmii2)

configure

1.uboot:

2.linux dts k3-j721e-common-proc-board.dts

&serdes_ln_ctrl {

idle-states = <J721E_SERDES0_LANE0_QSGMII_LANE1>, <J721E_SERDES0_LANE1_QSGMII_LANE2>,

<J721E_SERDES1_LANE0_PCIE1_LANE0>, <J721E_SERDES1_LANE1_PCIE1_LANE1>,

<J721E_SERDES2_LANE0_PCIE2_LANE0>, <J721E_SERDES2_LANE1_PCIE2_LANE1>,

<J721E_SERDES3_LANE0_USB3_0_SWAP>, <J721E_SERDES3_LANE1_USB3_0>,

<J721E_SERDES4_LANE0_EDP_LANE0>, <J721E_SERDES4_LANE1_EDP_LANE1>,

<J721E_SERDES4_LANE2_EDP_LANE2>, <J721E_SERDES4_LANE3_EDP_LANE3>;

};

&serdes_wiz0 {

status = "okay";

};

&serdes0 {

status = "okay";

assigned-clocks = <&serdes0 CDNS_SIERRA_PLL_CMNLC>, <&serdes0 CDNS_SIERRA_PLL_CMNLC1>;

assigned-clock-parents = <&wiz0_pll1_refclk>, <&wiz0_pll1_refclk>;

#address-cells = <1>;

#size-cells = <0>;

serdes0_sgmii_link: phy@0 {

reg = <0>;

cdns,num-lanes = <2>;

#phy-cells = <0>;

cdns,phy-type = <PHY_TYPE_SGMII>;

resets = <&serdes_wiz0 1>,<&serdes_wiz0 2>;

};

};

&cpsw0 {

status = "okay";

};

&cpsw0_port2 {

status = "okay";

phy-handle = <&cpsw9g_phy1>;

phy-mode = "sgmii";

mac-address = [00 00 00 00 00 00];

phys = <&cpsw0_phy_gmii_sel 2>,<&serdes0_sgmii_link>;

phy-names = "portmode", "serdes-phy";

};

&cpsw9g_mdio {

status = "okay";

pinctrl-names = "default";

pinctrl-0 = <&mdio0_pins_default>;

reset-post-delay-us = <120000>;

#address-cells = <1>;

#size-cells = <0>;

cpsw9g_phy1: ethernet-phy@1 {

reg = <1>;

compatible = "ethernet-phy-id001c.cb30","ethernet-phy-ieee802.3-c22";

fixed-link {

speed = <1000>;

full-duplex;

};

};

};

3.remove j7-main-r5f0_0-fw

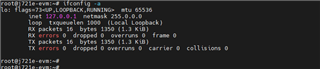

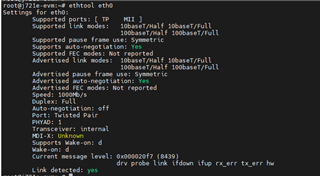

4. ethtool eth0

5.boot log

[ 0.000000] Booting Linux on physical CPU 0x0000000000 [0x411fd080] [ 0.000000] Linux version 6.6.32-ti-gdb8871293143-dirty (bingo@ubuntu) (aarch64-oe-linux-gcc (GCC) 13.3.0, GNU ld (GNU Binutils) 2.42.0.20240620) #29 SMP PREEMPT Thu Nov 14 14:39:50 CST 2024 [ 0.000000] KASLR disabled due to lack of seed [ 0.000000] Machine model: Texas Instruments J721e EVM [ 0.000000] earlycon: ns16550a0 at MMIO32 0x0000000002800000 (options '') [ 0.000000] printk: bootconsole [ns16550a0] enabled [ 0.000000] efi: UEFI not found. [ 0.000000] Reserved memory: created CMA memory pool at 0x00000008e0000000, size 512 MiB [ 0.000000] OF: reserved mem: initialized node linux,cma, compatible id shared-dma-pool [ 0.000000] OF: reserved mem: 0x00000008e0000000..0x00000008ffffffff (524288 KiB) map reusable linux,cma [ 0.000000] OF: reserved mem: 0x000000009e800000..0x000000009fffffff (24576 KiB) nomap non-reusable optee@9e800000 [ 0.000000] Reserved memory: created DMA memory pool at 0x00000000a0000000, size 1 MiB [ 0.000000] OF: reserved mem: initialized node vision-apps-r5f-dma-memory@a0000000, compatible id shared-dma-pool [ 0.000000] OF: reserved mem: 0x00000000a0000000..0x00000000a00fffff (1024 KiB) nomap non-reusable vision-apps-r5f-dma-memory@a0000000 [ 0.000000] Reserved memory: created DMA memory pool at 0x00000000a0100000, size 15 MiB [ 0.000000] OF: reserved mem: initialized node vision-apps-r5f-memory@a0100000, compatible id shared-dma-pool [ 0.000000] OF: reserved mem: 0x00000000a0100000..0x00000000a0ffffff (15360 KiB) nomap non-reusable vision-apps-r5f-memory@a0100000 [ 0.000000] Reserved memory: created DMA memory pool at 0x00000000a1000000, size 1 MiB [ 0.000000] OF: reserved mem: initialized node vision-apps-r5f-dma-memory@a1000000, compatible id shared-dma-pool [ 0.000000] OF: reserved mem: 0x00000000a1000000..0x00000000a10fffff (1024 KiB) nomap non-reusable vision-apps-r5f-dma-memory@a1000000 [ 0.000000] Reserved memory: created DMA memory pool at 0x00000000a1100000, size 15 MiB [ 0.000000] OF: reserved mem: initialized node vision-apps-r5f-memory@a1100000, compatible id shared-dma-pool [ 0.000000] OF: reserved mem: 0x00000000a1100000..0x00000000a1ffffff (15360 KiB) nomap non-reusable vision-apps-r5f-memory@a1100000 [ 0.000000] Reserved memory: created DMA memory pool at 0x00000000a2000000, size 1 MiB [ 0.000000] OF: reserved mem: initialized node vision-apps-r5f-dma-memory@a2000000, compatible id shared-dma-pool [ 0.000000] OF: reserved mem: 0x00000000a2000000..0x00000000a20fffff (1024 KiB) nomap non-reusable vision-apps-r5f-dma-memory@a2000000 [ 0.000000] Reserved memory: created DMA memory pool at 0x00000000a2100000, size 31 MiB [ 0.000000] OF: reserved mem: initialized node vision-apps-r5f-memory@a2100000, compatible id shared-dma-pool [ 0.000000] OF: reserved mem: 0x00000000a2100000..0x00000000a3ffffff (31744 KiB) nomap non-reusable vision-apps-r5f-memory@a2100000 [ 0.000000] Reserved memory: created DMA memory pool at 0x00000000a4000000, size 1 MiB [ 0.000000] OF: reserved mem: initialized node vision-apps-r5f-dma-memory@a4000000, compatible id shared-dma-pool [ 0.000000] OF: reserved mem: 0x00000000a4000000..0x00000000a40fffff (1024 KiB) nomap non-reusable vision-apps-r5f-dma-memory@a4000000 [ 0.000000] Reserved memory: created DMA memory pool at 0x00000000a4100000, size 31 MiB [ 0.000000] OF: reserved mem: initialized node vision-apps-r5f-memory@a4100000, compatible id shared-dma-pool [ 0.000000] OF: reserved mem: 0x00000000a4100000..0x00000000a5ffffff (31744 KiB) nomap non-reusable vision-apps-r5f-memory@a4100000 [ 0.000000] Reserved memory: created DMA memory pool at 0x00000000a6000000, size 1 MiB [ 0.000000] OF: reserved mem: initialized node vision-apps-r5f-dma-memory@a6000000, compatible id shared-dma-pool [ 0.000000] OF: reserved mem: 0x00000000a6000000..0x00000000a60fffff (1024 KiB) nomap non-reusable vision-apps-r5f-dma-memory@a6000000 [ 0.000000] Reserved memory: created DMA memory pool at 0x00000000a6100000, size 15 MiB [ 0.000000] OF: reserved mem: initialized node vision-apps-r5f-memory@a6100000, compatible id shared-dma-pool [ 0.000000] OF: reserved mem: 0x00000000a6100000..0x00000000a6ffffff (15360 KiB) nomap non-reusable vision-apps-r5f-memory@a6100000 [ 0.000000] Reserved memory: created DMA memory pool at 0x00000000a7000000, size 1 MiB [ 0.000000] OF: reserved mem: initialized node vision-apps-r5f-dma-memory@a7000000, compatible id shared-dma-pool [ 0.000000] OF: reserved mem: 0x00000000a7000000..0x00000000a70fffff (1024 KiB) nomap non-reusable vision-apps-r5f-dma-memory@a7000000 [ 0.000000] Reserved memory: created DMA memory pool at 0x00000000a7100000, size 15 MiB [ 0.000000] OF: reserved mem: initialized node vision-apps-r5f-memory@a7100000, compatible id shared-dma-pool [ 0.000000] OF: reserved mem: 0x00000000a7100000..0x00000000a7ffffff (15360 KiB) nomap non-reusable vision-apps-r5f-memory@a7100000 [ 0.000000] Reserved memory: created DMA memory pool at 0x00000000a8000000, size 1 MiB [ 0.000000] OF: reserved mem: initialized node vision-apps-c66-dma-memory@a8000000, compatible id shared-dma-pool [ 0.000000] OF: reserved mem: 0x00000000a8000000..0x00000000a80fffff (1024 KiB) nomap non-reusable vision-apps-c66-dma-memory@a8000000 [ 0.000000] Reserved memory: created DMA memory pool at 0x00000000a8100000, size 15 MiB [ 0.000000] OF: reserved mem: initialized node vision-apps-c66-memory@a8100000, compatible id shared-dma-pool [ 0.000000] OF: reserved mem: 0x00000000a8100000..0x00000000a8ffffff (15360 KiB) nomap non-reusable vision-apps-c66-memory@a8100000 [ 0.000000] Reserved memory: created DMA memory pool at 0x00000000a9000000, size 1 MiB [ 0.000000] OF: reserved mem: initialized node vision-apps-c66-dma-memory@a9000000, compatible id shared-dma-pool [ 0.000000] OF: reserved mem: 0x00000000a9000000..0x00000000a90fffff (1024 KiB) nomap non-reusable vision-apps-c66-dma-memory@a9000000 [ 0.000000] Reserved memory: created DMA memory pool at 0x00000000a9100000, size 15 MiB [ 0.000000] OF: reserved mem: initialized node vision-apps-c66-memory@a9100000, compatible id shared-dma-pool [ 0.000000] OF: reserved mem: 0x00000000a9100000..0x00000000a9ffffff (15360 KiB) nomap non-reusable vision-apps-c66-memory@a9100000 [ 0.000000] OF: reserved mem: 0x00000000aa000000..0x00000000abffffff (32768 KiB) nomap non-reusable vision-apps-rtos-ipc-memory-region [ 0.000000] Reserved memory: created DMA memory pool at 0x00000000ac000000, size 96 MiB [ 0.000000] OF: reserved mem: initialized node vision-apps-dma-memory@ac000000, compatible id shared-dma-pool [ 0.000000] OF: reserved mem: 0x00000000ac000000..0x00000000b1ffffff (98304 KiB) nomap non-reusable vision-apps-dma-memory@ac000000 [ 0.000000] Reserved memory: created DMA memory pool at 0x00000000b2000000, size 1 MiB [ 0.000000] OF: reserved mem: initialized node vision-apps-c71-dma-memory@b2000000, compatible id shared-dma-pool [ 0.000000] OF: reserved mem: 0x00000000b2000000..0x00000000b20fffff (1024 KiB) nomap non-reusable vision-apps-c71-dma-memory@b2000000 [ 0.000000] Reserved memory: created DMA memory pool at 0x00000000b2100000, size 95 MiB [ 0.000000] OF: reserved mem: initialized node vision-apps-c71-memory@b2100000, compatible id shared-dma-pool [ 0.000000] OF: reserved mem: 0x00000000b2100000..0x00000000b7ffffff (97280 KiB) nomap non-reusable vision-apps-c71-memory@b2100000 [ 0.000000] OF: reserved mem: initialized node vision_apps_shared-memories, compatible id dma-heap-carveout [ 0.000000] OF: reserved mem: 0x00000000b8000000..0x00000000d7ffffff (524288 KiB) map non-reusable vision_apps_shared-memories [ 0.000000] Reserved memory: created DMA memory pool at 0x00000000d8000000, size 192 MiB [ 0.000000] OF: reserved mem: initialized node vision-apps-core-heap-memory-lo@d8000000, compatible id shared-dma-pool [ 0.000000] OF: reserved mem: 0x00000000d8000000..0x00000000e3ffffff (196608 KiB) nomap non-reusable vision-apps-core-heap-memory-lo@d8000000 [ 0.000000] Reserved memory: created DMA memory pool at 0x00000000e4000000, size 8 MiB [ 0.000000] OF: reserved mem: initialized node vision-apps-r5f-virtual-eth-queues@e4000000, compatible id shared-dma-pool [ 0.000000] OF: reserved mem: 0x00000000e4000000..0x00000000e47fffff (8192 KiB) nomap non-reusable vision-apps-r5f-virtual-eth-queues@e4000000 [ 0.000000] Reserved memory: created DMA memory pool at 0x00000000e4800000, size 24 MiB [ 0.000000] OF: reserved mem: initialized node vision-apps-r5f-virtual-eth-buffers@e4800000, compatible id shared-dma-pool [ 0.000000] OF: reserved mem: 0x00000000e4800000..0x00000000e5ffffff (24576 KiB) nomap non-reusable vision-apps-r5f-virtual-eth-buffers@e4800000 [ 0.000000] Reserved memory: created DMA memory pool at 0x0000000880000000, size 624 MiB [ 0.000000] OF: reserved mem: initialized node vision-apps-core-heap-memory-hi@880000000, compatible id shared-dma-pool [ 0.000000] OF: reserved mem: 0x0000000880000000..0x00000008a6ffffff (638976 KiB) nomap non-reusable vision-apps-core-heap-memory-hi@880000000 [ 0.000000] Zone ranges: [ 0.000000] DMA [mem 0x0000000080000000-0x00000000ffffffff] [ 0.000000] DMA32 empty [ 0.000000] Normal [mem 0x0000000100000000-0x00000008ffffffff] [ 0.000000] Movable zone start for each node [ 0.000000] Early memory node ranges [ 0.000000] node 0: [mem 0x0000000080000000-0x000000009e7fffff] [ 0.000000] node 0: [mem 0x000000009e800000-0x00000000b7ffffff] [ 0.000000] node 0: [mem 0x00000000b8000000-0x00000000d7ffffff] [ 0.000000] node 0: [mem 0x00000000d8000000-0x00000000e5ffffff] [ 0.000000] node 0: [mem 0x00000000e6000000-0x00000000ffffffff] [ 0.000000] node 0: [mem 0x0000000880000000-0x00000008a6ffffff] [ 0.000000] node 0: [mem 0x00000008a7000000-0x00000008ffffffff] [ 0.000000] Initmem setup node 0 [mem 0x0000000080000000-0x00000008ffffffff] [ 0.000000] psci: probing for conduit method from DT. [ 0.000000] psci: PSCIv1.1 detected in firmware. [ 0.000000] psci: Using standard PSCI v0.2 function IDs [ 0.000000] psci: Trusted OS migration not required [ 0.000000] psci: SMC Calling Convention v1.4 [ 0.000000] percpu: Embedded 20 pages/cpu s42920 r8192 d30808 u81920 [ 0.000000] pcpu-alloc: s42920 r8192 d30808 u81920 alloc=20*4096 [ 0.000000] pcpu-alloc: [0] 0 [0] 1 [ 0.000000] Detected PIPT I-cache on CPU0 [ 0.000000] CPU features: detected: GIC system register CPU interface [ 0.000000] CPU features: detected: Spectre-v3a [ 0.000000] CPU features: detected: Spectre-BHB [ 0.000000] CPU features: detected: ARM erratum 1742098 [ 0.000000] CPU features: detected: ARM errata 1165522, 1319367, or 1530923 [ 0.000000] alternatives: applying boot alternatives [ 0.000000] Kernel command line: console=ttyS2,115200n8 earlycon=ns16550a,mmio32,0x02800000 root=PARTUUID=076c4a2a-02 rw rootfstype=ext4 rootwait [ 0.000000] Dentry cache hash table entries: 524288 (order: 10, 4194304 bytes, linear) [ 0.000000] Inode-cache hash table entries: 262144 (order: 9, 2097152 bytes, linear) [ 0.000000] Built 1 zonelists, mobility grouping on. Total pages: 1032192 [ 0.000000] mem auto-init: stack:all(zero), heap alloc:off, heap free:off [ 0.000000] software IO TLB: area num 2. [ 0.000000] software IO TLB: mapped [mem 0x00000000fbfff000-0x00000000fffff000] (64MB) [ 0.000000] Memory: 1694808K/4194304K available (11904K kernel code, 1244K rwdata, 4016K rodata, 2432K init, 436K bss, 1975208K reserved, 524288K cma-reserved) [ 0.000000] SLUB: HWalign=64, Order=0-3, MinObjects=0, CPUs=2, Nodes=1 [ 0.000000] rcu: Preemptible hierarchical RCU implementation. [ 0.000000] rcu: RCU event tracing is enabled. [ 0.000000] rcu: RCU restricting CPUs from NR_CPUS=256 to nr_cpu_ids=2. [ 0.000000] Trampoline variant of Tasks RCU enabled. [ 0.000000] Tracing variant of Tasks RCU enabled. [ 0.000000] rcu: RCU calculated value of scheduler-enlistment delay is 25 jiffies. [ 0.000000] rcu: Adjusting geometry for rcu_fanout_leaf=16, nr_cpu_ids=2 [ 0.000000] NR_IRQS: 64, nr_irqs: 64, preallocated irqs: 0 [ 0.000000] GICv3: GIC: Using split EOI/Deactivate mode [ 0.000000] GICv3: 960 SPIs implemented [ 0.000000] GICv3: 0 Extended SPIs implemented [ 0.000000] Root IRQ handler: gic_handle_irq [ 0.000000] GICv3: GICv3 features: 16 PPIs [ 0.000000] GICv3: CPU0: found redistributor 0 region 0:0x0000000001900000 [ 0.000000] ITS [mem 0x01820000-0x0182ffff] [ 0.000000] GIC: enabling workaround for ITS: Socionext Synquacer pre-ITS [ 0.000000] ITS@0x0000000001820000: Devices Table too large, reduce ids 20->19 [ 0.000000] ITS@0x0000000001820000: allocated 524288 Devices @8a7800000 (flat, esz 8, psz 64K, shr 0) [ 0.000000] ITS: using cache flushing for cmd queue [ 0.000000] GICv3: using LPI property table @0x00000008a7040000 [ 0.000000] GIC: using cache flushing for LPI property table [ 0.000000] GICv3: CPU0: using allocated LPI pending table @0x00000008a7050000 [ 0.000000] rcu: srcu_init: Setting srcu_struct sizes based on contention. [ 0.000000] arch_timer: cp15 timer(s) running at 200.00MHz (phys). [ 0.000000] clocksource: arch_sys_counter: mask: 0x3ffffffffffffff max_cycles: 0x2e2049d3e8, max_idle_ns: 440795210634 ns [ 0.000000] sched_clock: 58 bits at 200MHz, resolution 5ns, wraps every 4398046511102ns [ 0.008413] Console: colour dummy device 80x25 [ 0.012979] Calibrating delay loop (skipped), value calculated using timer frequency.. 400.00 BogoMIPS (lpj=800000) [ 0.023650] pid_max: default: 32768 minimum: 301 [ 0.028398] LSM: initializing lsm=capability,integrity [ 0.033693] Mount-cache hash table entries: 8192 (order: 4, 65536 bytes, linear) [ 0.041263] Mountpoint-cache hash table entries: 8192 (order: 4, 65536 bytes, linear) [ 0.050050] RCU Tasks: Setting shift to 1 and lim to 1 rcu_task_cb_adjust=1. [ 0.057304] RCU Tasks Trace: Setting shift to 1 and lim to 1 rcu_task_cb_adjust=1. [ 0.065134] rcu: Hierarchical SRCU implementation. [ 0.070031] rcu: Max phase no-delay instances is 1000. [ 0.075553] Platform MSI: msi-controller@1820000 domain created [ 0.081810] PCI/MSI: /bus@100000/interrupt-controller@1800000/msi-controller@1820000 domain created [ 0.091247] EFI services will not be available. [ 0.095988] smp: Bringing up secondary CPUs ... [ 0.109191] Detected PIPT I-cache on CPU1 [ 0.109237] GICv3: CPU1: found redistributor 1 region 0:0x0000000001920000 [ 0.109248] GICv3: CPU1: using allocated LPI pending table @0x00000008a7060000 [ 0.109277] CPU1: Booted secondary processor 0x0000000001 [0x411fd080] [ 0.109329] smp: Brought up 1 node, 2 CPUs [ 0.138674] SMP: Total of 2 processors activated. [ 0.143479] CPU features: detected: 32-bit EL0 Support [ 0.148732] CPU features: detected: CRC32 instructions [ 0.154008] CPU: All CPU(s) started at EL2 [ 0.158190] alternatives: applying system-wide alternatives [ 0.164718] devtmpfs: initialized [ 0.174987] clocksource: jiffies: mask: 0xffffffff max_cycles: 0xffffffff, max_idle_ns: 7645041785100000 ns [ 0.184965] futex hash table entries: 512 (order: 3, 32768 bytes, linear) [ 0.197945] pinctrl core: initialized pinctrl subsystem [ 0.203571] DMI not present or invalid. [ 0.207904] NET: Registered PF_NETLINK/PF_ROUTE protocol family [ 0.214411] DMA: preallocated 512 KiB GFP_KERNEL pool for atomic allocations [ 0.221711] DMA: preallocated 512 KiB GFP_KERNEL|GFP_DMA pool for atomic allocations [ 0.229707] DMA: preallocated 512 KiB GFP_KERNEL|GFP_DMA32 pool for atomic allocations [ 0.237827] audit: initializing netlink subsys (disabled) [ 0.243429] audit: type=2000 audit(0.156:1): state=initialized audit_enabled=0 res=1 [ 0.243625] thermal_sys: Registered thermal governor 'step_wise' [ 0.251348] thermal_sys: Registered thermal governor 'power_allocator' [ 0.257501] cpuidle: using governor menu [ 0.268240] hw-breakpoint: found 6 breakpoint and 4 watchpoint registers. [ 0.275197] ASID allocator initialised with 65536 entries [ 0.291167] platform a40000.pinctrl: Fixed dependency cycle(s) with /bus@100000/pinctrl@a40000/mcu-cpsw-cpts [ 0.302716] Modules: 27712 pages in range for non-PLT usage [ 0.302721] Modules: 519232 pages in range for PLT usage [ 0.308813] HugeTLB: registered 1.00 GiB page size, pre-allocated 0 pages [ 0.321180] HugeTLB: 0 KiB vmemmap can be freed for a 1.00 GiB page [ 0.327582] HugeTLB: registered 32.0 MiB page size, pre-allocated 0 pages [ 0.334517] HugeTLB: 0 KiB vmemmap can be freed for a 32.0 MiB page [ 0.340918] HugeTLB: registered 2.00 MiB page size, pre-allocated 0 pages [ 0.347852] HugeTLB: 0 KiB vmemmap can be freed for a 2.00 MiB page [ 0.354253] HugeTLB: registered 64.0 KiB page size, pre-allocated 0 pages [ 0.361187] HugeTLB: 0 KiB vmemmap can be freed for a 64.0 KiB page [ 0.368271] k3-chipinfo 43000014.chipid: Family:J721E rev:SR1.1 JTAGID[0x1bb6402f] Detected [ 0.377398] iommu: Default domain type: Translated [ 0.382320] iommu: DMA domain TLB invalidation policy: strict mode [ 0.388752] SCSI subsystem initialized [ 0.392670] libata version 3.00 loaded. [ 0.392746] usbcore: registered new interface driver usbfs [ 0.398365] usbcore: registered new interface driver hub [ 0.403811] usbcore: registered new device driver usb [ 0.409215] pps_core: LinuxPPS API ver. 1 registered [ 0.414287] pps_core: Software ver. 5.3.6 - Copyright 2005-2007 Rodolfo Giometti <giometti@linux.it> [ 0.423626] PTP clock support registered [ 0.427730] EDAC MC: Ver: 3.0.0 [ 0.431154] scmi_core: SCMI protocol bus registered [ 0.436270] FPGA manager framework [ 0.439781] Advanced Linux Sound Architecture Driver Initialized. [ 0.446470] clocksource: Switched to clocksource arch_sys_counter [ 0.452810] VFS: Disk quotas dquot_6.6.0 [ 0.456832] VFS: Dquot-cache hash table entries: 512 (order 0, 4096 bytes) [ 0.466990] Carveout Heap: Exported 512 MiB at 0x00000000b8000000 [ 0.473282] NET: Registered PF_INET protocol family [ 0.478403] IP idents hash table entries: 65536 (order: 7, 524288 bytes, linear) [ 0.487318] tcp_listen_portaddr_hash hash table entries: 2048 (order: 3, 32768 bytes, linear) [ 0.496073] Table-perturb hash table entries: 65536 (order: 6, 262144 bytes, linear) [ 0.503995] TCP established hash table entries: 32768 (order: 6, 262144 bytes, linear) [ 0.512196] TCP bind hash table entries: 32768 (order: 8, 1048576 bytes, linear) [ 0.520632] TCP: Hash tables configured (established 32768 bind 32768) [ 0.527413] UDP hash table entries: 2048 (order: 4, 65536 bytes, linear) [ 0.534322] UDP-Lite hash table entries: 2048 (order: 4, 65536 bytes, linear) [ 0.541741] NET: Registered PF_UNIX/PF_LOCAL protocol family [ 0.547798] RPC: Registered named UNIX socket transport module. [ 0.553853] RPC: Registered udp transport module. [ 0.558659] RPC: Registered tcp transport module. [ 0.563462] RPC: Registered tcp-with-tls transport module. [ 0.569065] RPC: Registered tcp NFSv4.1 backchannel transport module. [ 0.575647] NET: Registered PF_XDP protocol family [ 0.580549] PCI: CLS 0 bytes, default 64 [ 0.585116] Initialise system trusted keyrings [ 0.589748] workingset: timestamp_bits=46 max_order=20 bucket_order=0 [ 0.596488] squashfs: version 4.0 (2009/01/31) Phillip Lougher [ 0.602578] NFS: Registering the id_resolver key type [ 0.607764] Key type id_resolver registered [ 0.612036] Key type id_legacy registered [ 0.616139] nfs4filelayout_init: NFSv4 File Layout Driver Registering... [ 0.622988] nfs4flexfilelayout_init: NFSv4 Flexfile Layout Driver Registering... [ 0.644363] Key type asymmetric registered [ 0.648547] Asymmetric key parser 'x509' registered [ 0.653551] Block layer SCSI generic (bsg) driver version 0.4 loaded (major 244) [ 0.661111] io scheduler mq-deadline registered [ 0.665741] io scheduler kyber registered [ 0.669850] io scheduler bfq registered [ 0.675783] pinctrl-single 4301c000.pinctrl: 94 pins, size 376 [ 0.682118] pinctrl-single 11c000.pinctrl: 173 pins, size 692 [ 0.688398] pinctrl-single 104200.pinctrl: 20 pins, size 80 [ 0.694155] pinctrl-single 104280.pinctrl: 8 pins, size 32 [ 0.700115] pinctrl-single a40000.pinctrl: 512 pins, size 2048 [ 0.709669] Serial: 8250/16550 driver, 12 ports, IRQ sharing enabled [ 0.718644] arm-smmu-v3 36600000.iommu: ias 48-bit, oas 48-bit (features 0x00001faf) [ 0.726826] arm-smmu-v3 36600000.iommu: allocated 65536 entries for cmdq [ 0.733934] arm-smmu-v3 36600000.iommu: allocated 32768 entries for evtq [ 0.741725] arm-smmu-v3 36600000.iommu: msi_domain absent - falling back to wired irqs [ 0.752428] loop: module loaded [ 0.756165] megasas: 07.725.01.00-rc1 [ 0.761679] tun: Universal TUN/TAP device driver, 1.6 [ 0.767375] VFIO - User Level meta-driver version: 0.3 [ 0.773232] usbcore: registered new interface driver usb-storage [ 0.779700] i2c_dev: i2c /dev entries driver [ 0.784701] sdhci: Secure Digital Host Controller Interface driver [ 0.791021] sdhci: Copyright(c) Pierre Ossman [ 0.795586] sdhci-pltfm: SDHCI platform and OF driver helper [ 0.801687] ledtrig-cpu: registered to indicate activity on CPUs [ 0.807995] SMCCC: SOC_ID: ARCH_SOC_ID not implemented, skipping .... [ 0.814821] usbcore: registered new interface driver usbhid [ 0.820516] usbhid: USB HID core driver [ 0.825187] hw perfevents: enabled with armv8_cortex_a72 PMU driver, 7 counters available [ 0.833795] optee: probing for conduit method. [ 0.838348] optee: revision 4.2 (12d7c4ee) [ 0.854765] optee: dynamic shared memory is enabled [ 0.864338] random: crng init done [ 0.867871] optee: initialized driver [ 0.872885] NET: Registered PF_PACKET protocol family [ 0.878097] Key type dns_resolver registered [ 0.885636] registered taskstats version 1 [ 0.889886] Loading compiled-in X.509 certificates [ 0.900563] ti-sci 44083000.system-controller: ABI: 4.0 (firmware rev 0x000a '10.0.8--v10.00.08 (Fiery Fox)') [ 1.001189] omap_i2c 42120000.i2c: bus 0 rev0.12 at 400 kHz [ 1.007512] pca953x 1-0020: supply vcc not found, using dummy regulator [ 1.014329] pca953x 1-0020: using no AI [ 2.022474] omap_i2c 2000000.i2c: timeout waiting for bus ready [ 2.028531] pca953x 1-0020: failed writing register [ 2.033572] pca953x: probe of 1-0020 failed with error -16 [ 2.039370] pca953x 1-0022: supply vcc not found, using dummy regulator [ 2.046185] pca953x 1-0022: using AI [ 3.054473] omap_i2c 2000000.i2c: timeout waiting for bus ready [ 3.060525] pca953x 1-0022: failed writing register [ 3.065559] pca953x: probe of 1-0022 failed with error -16 [ 3.071261] st_asm330lhh_i2c: probe of 1-006a failed with error -22 [ 3.077680] omap_i2c 2000000.i2c: bus 1 rev0.12 at 400 kHz [ 3.083811] pca953x 2-0020: supply vcc not found, using dummy regulator [ 3.090625] pca953x 2-0020: using no AI [ 3.118534] pca953x 2-0020: failed writing register [ 3.123562] pca953x: probe of 2-0020 failed with error -121 [ 3.129317] omap_i2c 2030000.i2c: bus 2 rev0.12 at 400 kHz [ 3.135053] ti-sci-intr 42200000.interrupt-controller: Interrupt Router 137 domain created [ 3.143596] ti-sci-intr bus@100000:interrupt-controller@a00000: Interrupt Router 131 domain created [ 3.152934] ti-sci-intr 310e0000.interrupt-controller: Interrupt Router 213 domain created [ 3.161531] ti-sci-inta 33d00000.interrupt-controller: Interrupt Aggregator domain 209 created [ 3.176836] k3-ringacc 2b800000.ringacc: Ring Accelerator probed rings:286, gp-rings[96,20] sci-dev-id:235 [ 3.186723] k3-ringacc 2b800000.ringacc: dma-ring-reset-quirk: disabled [ 3.193482] k3-ringacc 2b800000.ringacc: RA Proxy rev. 66346100, num_proxies:64 [ 3.203047] k3-ringacc 3c000000.ringacc: Ring Accelerator probed rings:1024, gp-rings[440,150] sci-dev-id:211 [ 3.213192] k3-ringacc 3c000000.ringacc: dma-ring-reset-quirk: disabled [ 3.219951] k3-ringacc 3c000000.ringacc: RA Proxy rev. 66346100, num_proxies:64 [ 3.227886] printk: console [ttyS2] disabled [ 3.232414] 2800000.serial: ttyS2 at MMIO 0x2800000 (irq = 204, base_baud = 3000000) is a 8250 [ 3.241296] printk: console [ttyS2] enabled [ 3.249792] printk: bootconsole [ns16550a0] disabled [ 3.263159] 2810000.serial: ttyS3 at MMIO 0x2810000 (irq = 205, base_baud = 3000000) is a 8250 [ 3.272316] 2840000.serial: ttyS6 at MMIO 0x2840000 (irq = 206, base_baud = 3000000) is a 8250 [ 3.282253] davinci_mdio c000f00.mdio: Configuring MDIO in manual mode [ 3.326474] davinci_mdio c000f00.mdio: davinci mdio revision 9.7, bus freq 1000000 [ 3.334896] davinci_mdio c000f00.mdio: phy[1]: device c000f00.mdio:01, driver RTL9010 PHY Driver [ 3.343685] am65-cpsw-nuss c000000.ethernet: initializing am65 cpsw nuss version 0x6BA01901, cpsw version 0x6BA80101 Ports: 9 quirks:00000000 [ 3.356454] am65-cpsw-nuss c000000.ethernet: Use random MAC address [ 3.362722] am65-cpsw-nuss c000000.ethernet: initialized cpsw ale version 1.4 [ 3.369842] am65-cpsw-nuss c000000.ethernet: ALE Table size 512 [ 3.376130] am65-cpsw-nuss c000000.ethernet: CPTS ver 0x4e8a010a, freq:200000000, add_val:4 pps:0 [ 3.387878] am65-cpts 310d0000.cpts: CPTS ver 0x4e8a010a, freq:200000000, add_val:4 pps:0 [ 3.396611] omap-mailbox 31f80000.mailbox: omap mailbox rev 0x66fc7100 [ 3.396856] mmc0: CQHCI version 5.10 [ 3.406721] omap-mailbox 31f81000.mailbox: omap mailbox rev 0x66fc7100 [ 3.413680] omap-mailbox 31f82000.mailbox: omap mailbox rev 0x66fc7100 [ 3.420505] omap-mailbox 31f83000.mailbox: omap mailbox rev 0x66fc7100 [ 3.427307] omap-mailbox 31f84000.mailbox: omap mailbox rev 0x66fc7100 [ 3.442501] mmc0: SDHCI controller on 4f80000.mmc [4f80000.mmc] using ADMA 64-bit [ 3.515731] mmc0: mmc_select_hs200 failed, error -110 [ 3.520789] mmc0: error -110 whilst initialising MMC card [ 3.637368] tps6594-rtc tps6594-rtc.4.auto: registered as rtc0 [ 3.641467] mmc0: mmc_select_hs200 failed, error -110 [ 3.648242] mmc0: error -110 whilst initialising MMC card [ 3.654428] tps6594-rtc tps6594-rtc.4.auto: setting system clock to 2024-02-28T15:35:24 UTC (1709134524) [ 3.786064] mmc0: mmc_select_hs200 failed, error -110 [ 3.791127] mmc0: error -110 whilst initialising MMC card [ 3.921892] ti-udma 285c0000.dma-controller: Channels: 26 (tchan: 13, rchan: 13, gp-rflow: 8) [ 3.933016] ti-udma 31150000.dma-controller: Channels: 122 (tchan: 61, rchan: 61, gp-rflow: 16) [ 3.946919] spi-nor spi0.0: unrecognized JEDEC id bytes: ff ff ff ff ff ff [ 3.954237] davinci_mdio c000f00.mdio: Configuring MDIO in manual mode [ 3.974759] mmc0: mmc_select_hs200 failed, error -110 [ 3.979806] mmc0: error -110 whilst initialising MMC card [ 3.986488] mmc0: Failed to initialize a non-removable card [ 3.998474] davinci_mdio c000f00.mdio: davinci mdio revision 9.7, bus freq 1000000 [ 4.012457] davinci_mdio c000f00.mdio: phy[1]: device c000f00.mdio:01, driver RTL9010 PHY Driver [ 4.021257] am65-cpsw-nuss c000000.ethernet: initializing am65 cpsw nuss version 0x6BA01901, cpsw version 0x6BA80101 Ports: 9 quirks:00000000 [ 4.034026] am65-cpsw-nuss c000000.ethernet: Use random MAC address [ 4.040291] am65-cpsw-nuss c000000.ethernet: initialized cpsw ale version 1.4 [ 4.047410] am65-cpsw-nuss c000000.ethernet: ALE Table size 512 [ 4.053668] am65-cpsw-nuss c000000.ethernet: CPTS ver 0x4e8a010a, freq:200000000, add_val:4 pps:0 [ 4.072633] am65-cpsw-nuss c000000.ethernet: set new flow-id-base 140 [ 4.084628] mmc1: CQHCI version 5.10 [ 4.091815] input: gpio-keys as /devices/platform/gpio-keys/input/input0 [ 4.098862] clk: Disabling unused clocks [ 4.121844] ALSA device list: [ 4.124813] No soundcards found. [ 4.129125] mmc1: SDHCI controller on 4fb0000.mmc [4fb0000.mmc] using ADMA 64-bit [ 4.136694] Waiting for root device PARTUUID=076c4a2a-02... [ 4.177849] tps6594 0-004c: Error IRQ trap overvoltage for LDO1 [ 4.186585] mmc1: new ultra high speed DDR50 SDHC card at address 59b4 [ 4.193438] mmcblk1: mmc1:59b4 EZSD1 29.1 GiB [ 4.199454] mmcblk1: p1 p2 [ 4.604108] EXT4-fs (mmcblk1p2): mounted filesystem b57c3b63-12a8-42de-8aac-e86cbb7e3fbc r/w with ordered data mode. Quota mode: none. [ 4.616265] VFS: Mounted root (ext4 filesystem) on device 179:2. [ 4.623297] devtmpfs: mounted [ 4.627253] Freeing unused kernel memory: 2432K [ 4.631859] Run /sbin/init as init process [ 4.635948] with arguments: [ 4.635949] /sbin/init [ 4.635951] with environment: [ 4.635953] HOME=/ [ 4.635955] TERM=linux [ 5.071944] ipv6: Unknown symbol make_kuid (err -2) [ 5.077047] ipv6: Unknown symbol __put_net (err -2) [ 5.082011] ipv6: Unknown symbol from_kuid_munged (err -2) [ 5.144070] systemd[1]: systemd 255.4^ running in system mode (+PAM -AUDIT -SELINUX -APPARMOR +IMA -SMACK +SECCOMP -GCRYPT -GNUTLS -OPENSSL +ACL +BLKID -CURL -ELFUTILS -FIDO2 -IDN2 -IDN -IPTC +KMOD -LIBCRYPTSETUP +LIBFDISK -PCRE2 -PWQUALITY -P11KIT -QRENCODE -TPM2 -BZIP2 -LZ4 -XZ -ZLIB +ZSTD -BPF_FRAMEWORK -XKBCOMMON +UTMP +SYSVINIT default-hierarchy=unified) [ 5.175839] systemd[1]: Detected architecture arm64. [ 5.202544] systemd[1]: Hostname set to <j721e-evm>. [ 5.451736] systemd[1]: Binding to IPv6 address not available since kernel does not support IPv6. [ 5.460628] systemd[1]: Binding to IPv6 address not available since kernel does not support IPv6. [ 5.494098] systemd[1]: /usr/lib/systemd/system/bt-enable.service:9: Standard output type syslog is obsolete, automatically updating to journal. Please update your unit file, and consider removing the setting altogether. [ 5.518106] systemd[1]: Configuration file /etc/systemd/system/app-init.service is marked executable. Please remove executable permission bits. Proceeding anyway. [ 5.594187] systemd[1]: /etc/systemd/system/sync-clocks.service:11: Standard output type syslog is obsolete, automatically updating to journal. Please update your unit file, and consider removing the setting altogether. [ 5.662210] systemd[1]: Queued start job for default target Graphical Interface. [ 5.701189] systemd[1]: Created slice Slice /system/getty. [ 5.723647] systemd[1]: Created slice Slice /system/modprobe. [ 5.747536] systemd[1]: Created slice Slice /system/serial-getty. [ 5.771288] systemd[1]: Created slice User and Session Slice. [ 5.794680] systemd[1]: Started Dispatch Password Requests to Console Directory Watch. [ 5.818610] systemd[1]: Started Forward Password Requests to Wall Directory Watch. [ 5.842549] systemd[1]: Expecting device /dev/ttyS2... [ 5.858578] systemd[1]: Reached target Path Units. [ 5.874531] systemd[1]: Reached target Remote File Systems. [ 5.894522] systemd[1]: Reached target Slice Units. [ 5.910527] systemd[1]: Reached target Swaps. [ 5.949051] systemd[1]: Listening on RPCbind Server Activation Socket. [ 5.974608] systemd[1]: Reached target RPC Port Mapper. [ 5.998175] systemd[1]: Listening on Process Core Dump Socket. [ 6.018700] systemd[1]: Listening on initctl Compatibility Named Pipe. [ 6.043092] systemd[1]: Listening on Journal Audit Socket. [ 6.066811] systemd[1]: Listening on Journal Socket (/dev/log). [ 6.086820] systemd[1]: Listening on Journal Socket. [ 6.102876] systemd[1]: Listening on Network Service Netlink Socket. [ 6.129939] systemd[1]: Listening on udev Control Socket. [ 6.150775] systemd[1]: Listening on udev Kernel Socket. [ 6.170778] systemd[1]: Listening on User Database Manager Socket. [ 6.214685] systemd[1]: Mounting Huge Pages File System... [ 6.232445] systemd[1]: Mounting POSIX Message Queue File System... [ 6.258767] systemd[1]: Mounting Kernel Debug File System... [ 6.264851] systemd[1]: Kernel Trace File System was skipped because of an unmet condition check (ConditionPathExists=/sys/kernel/tracing). [ 6.305801] systemd[1]: Mounting Temporary Directory /tmp... [ 6.334891] systemd[1]: Starting Create List of Static Device Nodes... [ 6.378937] systemd[1]: Starting Load Kernel Module configfs... [ 6.386999] systemd[1]: Starting Load Kernel Module drm... [ 6.402931] systemd[1]: Starting Load Kernel Module fuse... [ 6.427541] systemd[1]: Starting Start psplash boot splash screen... [ 6.438211] fuse: Unknown symbol make_kuid (err -2) [ 6.444716] fuse: Unknown symbol put_pid_ns (err -2) [ 6.450069] fuse: Unknown symbol from_kgid (err -2) [ 6.454972] fuse: Unknown symbol from_kuid (err -2) [ 6.459917] fuse: Unknown symbol current_in_userns (err -2) [ 6.459947] fuse: Unknown symbol make_kgid (err -2) [ 6.459956] fuse: Unknown symbol from_kgid_munged (err -2) [ 6.460014] fuse: Unknown symbol __put_user_ns (err -2) [ 6.460033] fuse: Unknown symbol from_kuid_munged (err -2) [ 6.483383] drm: Unknown symbol from_kuid_munged (err -2) [ 6.494871] systemd[1]: Starting RPC Bind... [ 6.514721] systemd[1]: File System Check on Root Device was skipped because of an unmet condition check (ConditionPathIsReadWrite=!/). [ 6.530917] systemd[1]: Starting Journal Service... [ 6.563226] ipv6: Unknown symbol make_kuid (err -2) [ 6.568318] ipv6: Unknown symbol __put_net (err -2) [ 6.573279] ipv6: Unknown symbol from_kuid_munged (err -2) [ 6.590941] systemd[1]: Starting Load Kernel Modules... [ 6.608945] ipv6: Unknown symbol make_kuid (err -2) [ 6.614095] ipv6: Unknown symbol __put_net (err -2) [ 6.620056] ipv6: Unknown symbol from_kuid_munged (err -2) [ 6.622894] systemd[1]: Starting Generate network units from Kernel command line... [ 6.626066] systemd-journald[108]: Collecting audit messages is enabled. [ 6.659065] systemd[1]: Starting Remount Root and Kernel File Systems... [ 6.673782] cryptodev: loading out-of-tree module taints kernel. [ 6.676312] ipv6: Unknown symbol make_kuid (err -2) [ 6.691178] ipv6: Unknown symbol __put_net (err -2) [ 6.696191] ipv6: Unknown symbol from_kuid_munged (err -2) [ 6.727474] systemd[1]: Starting Coldplug All udev Devices... [ 6.730772] cryptodev: driver 1.13 loaded. [ 6.761136] systemd[1]: Started Journal Service. [ 6.770894] EXT4-fs (mmcblk1p2): re-mounted b57c3b63-12a8-42de-8aac-e86cbb7e3fbc r/w. Quota mode: none. [ 7.170207] systemd-journald[108]: Received client request to flush runtime journal. [ 7.403821] audit: type=1334 audit(1709134528.248:2): prog-id=6 op=LOAD [ 7.410762] audit: type=1334 audit(1709134528.256:3): prog-id=7 op=LOAD [ 7.596593] audit: type=1334 audit(1709134528.440:4): prog-id=8 op=LOAD [ 7.629073] audit: type=1334 audit(1709134528.472:5): prog-id=9 op=LOAD [ 7.790936] audit: type=1334 audit(1709134528.636:6): prog-id=10 op=LOAD [ 7.803190] audit: type=1334 audit(1709134528.640:7): prog-id=11 op=LOAD [ 7.814773] audit: type=1334 audit(1709134528.640:8): prog-id=12 op=LOAD [ 8.261372] drm: Unknown symbol from_kuid_munged (err -2) [ 8.286766] kfifo_buf: exports duplicate symbol iio_kfifo_allocate (owned by kernel) [ 8.299337] pinctrl-single 11c000.pinctrl: pin PIN164 already requested by 601000.gpio; cannot claim for 4104000.cdns-usb [ 8.313788] pinctrl-single 11c000.pinctrl: pin-164 (4104000.cdns-usb) status -22 [ 8.321262] pinctrl-single 11c000.pinctrl: could not request pin 164 (PIN164) from group main-usbss0-default-pins on device pinctrl-single [ 8.333865] cdns3-ti 4104000.cdns-usb: Error applying setting, reverse things back [ 8.346011] drm: Unknown symbol from_kuid_munged (err -2) [ 8.363544] omap_rng 4e10000.rng: Random Number Generator ver. 241b34c [ 8.371774] mc: Linux media interface: v0.10 [ 8.372214] CAN device driver interface [ 8.384363] k3-dsp-rproc 4d80800000.dsp: assigned reserved memory node vision-apps-c66-dma-memory@a9000000 [ 8.402027] k3-dsp-rproc 4d80800000.dsp: configured DSP for IPC-only mode [ 8.415537] kfifo_buf: exports duplicate symbol iio_kfifo_allocate (owned by kernel) [ 8.427888] remoteproc remoteproc0: 4d80800000.dsp is available [ 8.434584] remoteproc remoteproc0: attaching to 4d80800000.dsp [ 8.447154] videodev: Linux video capture interface: v2.00 [ 8.461739] k3-dsp-rproc 4d80800000.dsp: DSP initialized in IPC-only mode [ 8.472181] kfifo_buf: exports duplicate symbol iio_kfifo_allocate (owned by kernel) [ 8.491116] rproc-virtio rproc-virtio.11.auto: assigned reserved memory node vision-apps-c66-dma-memory@a9000000 [ 8.523971] virtio_rpmsg_bus virtio0: rpmsg host is online [ 8.529503] virtio_rpmsg_bus virtio0: creating channel rpmsg_chrdev addr 0xd [ 8.543080] kfifo_buf: exports duplicate symbol iio_kfifo_allocate (owned by kernel) [ 8.559354] rproc-virtio rproc-virtio.11.auto: registered virtio0 (type 7) [ 8.576078] remoteproc remoteproc0: remote processor 4d80800000.dsp is now attached [ 8.585172] k3-dsp-rproc 4d81800000.dsp: assigned reserved memory node vision-apps-c66-dma-memory@a8000000 [ 8.598276] k3-dsp-rproc 4d81800000.dsp: configured DSP for IPC-only mode [ 8.608456] audit: type=1334 audit(1709134529.452:9): prog-id=13 op=LOAD [ 8.610849] remoteproc remoteproc1: 4d81800000.dsp is available [ 8.625514] remoteproc remoteproc1: attaching to 4d81800000.dsp [ 8.636850] k3-dsp-rproc 4d81800000.dsp: DSP initialized in IPC-only mode [ 8.645989] rproc-virtio rproc-virtio.14.auto: assigned reserved memory node vision-apps-c66-dma-memory@a8000000 [ 8.683628] platform 41000000.r5f: R5F core may have been powered on by a different host, programmed state (0) != actual state (1) [ 8.702924] platform 41000000.r5f: configured R5F for IPC-only mode [ 8.711093] platform 41000000.r5f: assigned reserved memory node vision-apps-r5f-dma-memory@a0000000 [ 8.715919] virtio_rpmsg_bus virtio1: rpmsg host is online [ 8.720298] virtio_rpmsg_bus virtio1: creating channel rpmsg_chrdev addr 0xd [ 8.734606] remoteproc remoteproc2: 41000000.r5f is available [ 8.744823] remoteproc remoteproc2: attaching to 41000000.r5f [ 8.747358] at24 0-0050: supply vcc not found, using dummy regulator [ 8.762540] rproc-virtio rproc-virtio.14.auto: registered virtio1 (type 7) [ 8.763804] platform 41000000.r5f: R5F core initialized in IPC-only mode [ 8.780047] rproc-virtio rproc-virtio.15.auto: assigned reserved memory node vision-apps-r5f-dma-memory@a0000000 [ 8.791501] virtio_rpmsg_bus virtio2: rpmsg host is online [ 8.792913] remoteproc remoteproc1: remote processor 4d81800000.dsp is now attached [ 8.804728] virtio_rpmsg_bus virtio2: creating channel ti.ipc4.ping-pong addr 0xd [ 8.811400] rproc-virtio rproc-virtio.15.auto: registered virtio2 (type 7) [ 8.812386] virtio_rpmsg_bus virtio2: creating channel rpmsg_chrdev addr 0xe [ 8.826145] remoteproc remoteproc2: remote processor 41000000.r5f is now attached [ 8.837198] platform 5c00000.r5f: configured R5F for remoteproc mode [ 8.850690] k3-dsp-rproc 64800000.dsp: assigned reserved memory node vision-apps-c71-dma-memory@b2000000 [ 8.863679] platform 5c00000.r5f: assigned reserved memory node vision-apps-r5f-dma-memory@a2000000 [ 8.874139] remoteproc remoteproc3: 5c00000.r5f is available [ 8.887411] remoteproc remoteproc3: Direct firmware load for j7-main-r5f0_0-fw failed with error -2 [ 8.898375] remoteproc remoteproc3: powering up 5c00000.r5f [ 8.906758] remoteproc remoteproc3: Direct firmware load for j7-main-r5f0_0-fw failed with error -2 [ 8.918796] remoteproc remoteproc3: request_firmware failed: -2 [ 8.939585] drm: Unknown symbol from_kuid_munged (err -2) [ 8.943918] img_enc 4200000.video-encoder: vxe_enc_probe: using heap 1 for internal alloc [ 8.953247] k3-dsp-rproc 64800000.dsp: configured DSP for IPC-only mode [ 8.953399] remoteproc remoteproc4: 64800000.dsp is available [ 8.953444] remoteproc remoteproc4: attaching to 64800000.dsp [ 8.953653] remoteproc remoteproc4: unsupported resource 65538 [ 8.971696] m_can_platform 40528000.can: registering can0 failed (err=-22) [ 8.993345] k3-dsp-rproc 64800000.dsp: DSP initialized in IPC-only mode [ 9.000477] rproc-virtio rproc-virtio.16.auto: assigned reserved memory node vision-apps-c71-dma-memory@b2000000 [ 9.011059] img_enc 4200000.video-encoder: encoder registered as /dev/video1 [ 9.013392] virtio_rpmsg_bus virtio3: creating channel rpmsg_chrdev addr 0xd [ 9.022632] m_can_platform: probe of 40528000.can failed with error -22 [ 9.032718] virtio_rpmsg_bus virtio3: rpmsg host is online [ 9.039776] m_can_platform 40568000.can: registering can0 failed (err=-22) [ 9.046674] drm: Unknown symbol from_kuid_munged (err -2) [ 9.049109] rproc-virtio rproc-virtio.16.auto: registered virtio3 (type 7) [ 9.059138] img_dec 4300000.video-decoder: decoder registered as /dev/video0 [ 9.059976] remoteproc remoteproc4: remote processor 64800000.dsp is now attached [ 9.082526] m_can_platform: probe of 40568000.can failed with error -22 [ 9.106765] m_can_platform 2721000.can: registering can0 failed (err=-22) [ 9.126699] m_can_platform: probe of 2721000.can failed with error -22 [ 9.167164] dbus-broker-lau[306]: memfd_create() called without MFD_EXEC or MFD_NOEXEC_SEAL set [ 9.181564] yaxon update start... [ 9.215467] Waiting for USB to be mounted... [ 9.256820] kfifo_buf: exports duplicate symbol iio_kfifo_allocate (owned by kernel) [ 9.279239] xhci-hcd xhci-hcd.17.auto: xHCI Host Controller [ 9.289448] xhci-hcd xhci-hcd.17.auto: new USB bus registered, assigned bus number 1 [ 9.304417] xhci-hcd xhci-hcd.17.auto: hcc params 0x200073c9 hci version 0x100 quirks 0x0000002000008010 [ 9.318969] xhci-hcd xhci-hcd.17.auto: irq 833, io mem 0x06410000 [ 9.326628] kfifo_buf: exports duplicate symbol iio_kfifo_allocate (owned by kernel) [ 9.327833] cdns-ufshcd 4e84000.ufs: ufshcd_populate_vreg: Unable to find vdd-hba-supply regulator, assuming enabled [ 9.334599] xhci-hcd xhci-hcd.17.auto: xHCI Host Controller [ 9.347607] cdns-ufshcd 4e84000.ufs: ufshcd_populate_vreg: Unable to find vcc-supply regulator, assuming enabled [ 9.362153] cdns-ufshcd 4e84000.ufs: ufshcd_populate_vreg: Unable to find vccq-supply regulator, assuming enabled [ 9.372930] cdns-ufshcd 4e84000.ufs: ufshcd_populate_vreg: Unable to find vccq2-supply regulator, assuming enabled [ 9.379569] remoteproc remoteproc5: b034000.pru is available [ 9.384772] xhci-hcd xhci-hcd.17.auto: new USB bus registered, assigned bus number 2 [ 9.396794] xhci-hcd xhci-hcd.17.auto: Host supports USB 3.0 SuperSpeed [ 9.404841] remoteproc remoteproc6: b004000.rtu is available [ 9.411984] hub 1-0:1.0: USB hub found [ 9.419199] remoteproc remoteproc7: b00a000.txpru is available [ 9.438222] hub 1-0:1.0: 1 port detected [ 9.442763] scsi host0: ufshcd [ 9.455599] usb usb2: We don't know the algorithms for LPM for this host, disabling LPM. [ 9.466835] hub 2-0:1.0: USB hub found [ 9.475458] remoteproc remoteproc8: b038000.pru is available [ 9.475847] hub 2-0:1.0: 1 port detected [ 9.498660] audit: type=1334 audit(1709134530.344:10): prog-id=14 op=LOAD [ 9.510730] remoteproc remoteproc9: b006000.rtu is available [ 9.516934] audit: type=1334 audit(1709134530.356:11): prog-id=15 op=LOAD [ 9.525375] remoteproc remoteproc10: b00c000.txpru is available [ 9.534839] remoteproc remoteproc11: b134000.pru is available [ 9.543561] remoteproc remoteproc12: b104000.rtu is available [ 9.544783] remoteproc remoteproc13: b10a000.txpru is available [ 9.546049] remoteproc remoteproc14: b138000.pru is available [ 9.547307] remoteproc remoteproc15: b106000.rtu is available [ 9.548506] remoteproc remoteproc16: b10c000.txpru is available [ 9.613055] ipv6: Unknown symbol make_kuid (err -2) [ 9.631054] ipv6: Unknown symbol __put_net (err -2) [ 9.643624] ipv6: Unknown symbol from_kuid_munged (err -2) [ 9.708020] ipv6: Unknown symbol make_kuid (err -2) [ 9.717637] ipv6: Unknown symbol __put_net (err -2) [ 9.723648] ipv6: Unknown symbol from_kuid_munged (err -2) [ 9.746461] ipv6: Unknown symbol make_kuid (err -2) [ 9.757386] ipv6: Unknown symbol __put_net (err -2) [ 9.765976] ipv6: Unknown symbol from_kuid_munged (err -2) [ 9.856470] cdns-ufshcd 4e84000.ufs: link startup failed 1 [ 9.862106] cdns-ufshcd 4e84000.ufs: UFS Host state=0 [ 9.867417] cdns-ufshcd 4e84000.ufs: outstanding reqs=0x0 tasks=0x0 [ 9.867423] cdns-ufshcd 4e84000.ufs: saved_err=0x0, saved_uic_err=0x0 [ 9.867426] cdns-ufshcd 4e84000.ufs: Device power mode=1, UIC link state=0 [ 9.867429] cdns-ufshcd 4e84000.ufs: PM in progress=0, sys. suspended=0 [ 9.867432] cdns-ufshcd 4e84000.ufs: Auto BKOPS=0, Host self-block=0 [ 9.867434] cdns-ufshcd 4e84000.ufs: Clk gate=1 [ 9.867437] cdns-ufshcd 4e84000.ufs: last_hibern8_exit_tstamp at 0 us, hibern8_exit_cnt=0 [ 9.867440] cdns-ufshcd 4e84000.ufs: last intr at 9856447 us, last intr status=0x404 [ 9.867443] cdns-ufshcd 4e84000.ufs: error handling flags=0x0, req. abort count=0 [ 9.867446] cdns-ufshcd 4e84000.ufs: hba->ufs_version=0x210, Host capabilities=0x1587031f, caps=0x0 [ 9.867449] cdns-ufshcd 4e84000.ufs: quirks=0x0, dev. quirks=0x0 [ 9.867452] cdns-ufshcd 4e84000.ufs: clk: core_clk, rate: 250000000 [ 9.867455] cdns-ufshcd 4e84000.ufs: clk: phy_clk, rate: 19200000 [ 9.867458] cdns-ufshcd 4e84000.ufs: clk: ref_clk, rate: 19200000 [ 9.867476] host_regs: 00000000: 1587031f 00000000 00000210 00000000 [ 9.867479] host_regs: 00000010: 00000000 00000000 00000000 00000000 [ 9.867482] host_regs: 00000020: 00000000 00000470 00000000 00000000 [ 9.867485] host_regs: 00000030: 00000008 00000001 00000000 00000000 [ 9.867487] host_regs: 00000040: 00000000 00000000 00000000 00000000 [ 9.867490] host_regs: 00000050: 00000000 00000000 00000000 00000000 [ 9.867492] host_regs: 00000060: 00000000 00000000 00000000 00000000 [ 9.867495] host_regs: 00000070: 00000000 00000000 00000000 00000000 [ 9.867497] host_regs: 00000080: 00000000 00000000 00000000 00000000 [ 9.867500] host_regs: 00000090: 00000016 00000000 00000001 00000000 [ 9.867503] cdns-ufshcd 4e84000.ufs: No record of pa_err [ 9.867506] cdns-ufshcd 4e84000.ufs: No record of dl_err [ 9.867509] cdns-ufshcd 4e84000.ufs: No record of nl_err [ 9.867511] cdns-ufshcd 4e84000.ufs: No record of tl_err [ 9.867513] cdns-ufshcd 4e84000.ufs: No record of dme_err [ 9.867515] cdns-ufshcd 4e84000.ufs: No record of auto_hibern8_err [ 9.867518] cdns-ufshcd 4e84000.ufs: No record of fatal_err [ 9.867520] cdns-ufshcd 4e84000.ufs: link_startup_fail[0] = 0x1 at 9856465 us [ 9.867523] cdns-ufshcd 4e84000.ufs: link_startup_fail: total cnt=1 [ 9.867526] cdns-ufshcd 4e84000.ufs: No record of resume_fail [ 9.867529] cdns-ufshcd 4e84000.ufs: No record of suspend_fail [ 9.867531] cdns-ufshcd 4e84000.ufs: No record of wlun resume_fail [ 9.867533] cdns-ufshcd 4e84000.ufs: No record of wlun suspend_fail [ 9.867535] cdns-ufshcd 4e84000.ufs: No record of dev_reset [ 9.867537] cdns-ufshcd 4e84000.ufs: No record of host_reset [ 9.867539] cdns-ufshcd 4e84000.ufs: No record of task_abort [ 9.880680] cdns-ufshcd 4e84000.ufs: ufshcd_async_scan failed: 1 [ 10.196880] cfg80211: Unknown symbol __put_net (err -2) [ 10.202522] cfg80211: Unknown symbol get_net_ns_by_fd (err -2) [ 10.246695] Update script not found [ 10.250320] yaxon update end [ 10.263116] bluetooth: Unknown symbol from_kuid (err -2) [ 10.268585] bluetooth: Unknown symbol from_kgid_munged (err -2) [ 10.274651] bluetooth: Unknown symbol from_kuid_munged (err -2) [ 10.519296] rtl9010_init_phy: RTL9010 mode= 4 neg= 0 speed =1000 dup=1 ============ [ 10.594699] overlay: Unknown symbol from_kgid (err -2) [ 10.610924] overlay: Unknown symbol from_kuid (err -2) [ 10.618158] rtl9010_hardware_reset success! [ 10.624013] RTL9010Ax_Initial_Configuration: RTL9010 ============ [ 10.637904] RTL9010Ax_Initial_Configuration_Check: RTL9010 ============ [ 10.649651] RTL9010Ax_Initial_with_SGMII_Configuration: RTL9010 ============ [ 10.649741] ipv6: Unknown symbol make_kuid (err -2) [ 10.665163] ipv6: Unknown symbol __put_net (err -2) [ 10.670569] ipv6: Unknown symbol from_kuid_munged (err -2) [ 10.699350] RTL9010Ax_Initial_with_SGMII_Configuration_Check: RTL9010 ============ [ 10.788743] RTL9010Ax_Soft_Reset: RTL9010 ============ [ 10.794413] rtl9010_config_init:RTL9010 phy driver config init end. [ 10.800706] rtl9010_init_phy: RTL9010 mode= 4 neg= 0 speed =1000 dup=1 ============ [ 10.808366] rtl9010_power_on:GPIO_PHY_VSYS request. [ 10.813242] rtl9010_power_on:GPIO_PHY_POWER request . [ 10.818336] rtl9010_power_on:GPIO_PHY_RESET request . [ 10.882500] k3_r5_rproc bus@100000:r5fss@5c00000: Timed out waiting for 5c00000.r5f core to power up! [ 10.900211] platform 5e00000.r5f: configured R5F for remoteproc mode [ 10.915222] platform 5e00000.r5f: assigned reserved memory node vision-apps-r5f-dma-memory@a6000000 [ 10.925942] rtl9010_hardware_reset success! [ 10.930393] RTL9010Ax_Initial_Configuration: RTL9010 ============ [ 10.937655] remoteproc remoteproc17: 5e00000.r5f is available [ 10.949751] RTL9010Ax_Initial_Configuration_Check: RTL9010 ============ [ 10.971598] RTL9010Ax_Initial_with_SGMII_Configuration: RTL9010 ============ [ 11.023034] RTL9010Ax_Initial_with_SGMII_Configuration_Check: RTL9010 ============ [ 11.030761] remoteproc remoteproc17: loading /lib/firmware/j7-main-r5f1_0-fw failed with error -22 [ 11.042894] remoteproc remoteproc17: Direct firmware load for j7-main-r5f1_0-fw failed with error -22 [ 11.058527] remoteproc remoteproc17: powering up 5e00000.r5f [ 11.068368] remoteproc remoteproc17: loading /lib/firmware/j7-main-r5f1_0-fw failed with error -22 [ 11.082527] remoteproc remoteproc17: Direct firmware load for j7-main-r5f1_0-fw failed with error -22 [ 11.097998] remoteproc remoteproc17: request_firmware failed: -22 [ 11.166347] RTL9010Ax_Soft_Reset: RTL9010 ============ [ 11.172176] am65-cpsw-nuss c000000.ethernet eth0: PHY [c000f00.mdio:01] driver [RTL9010 PHY Driver] (irq=POLL) [ 11.187479] am65-cpsw-nuss c000000.ethernet eth0: configuring for phy/sgmii link mode [ 11.187495] rtl9010_init_phy: RTL9010 mode= 4 neg= 0 speed =1000 dup=1 ============ [ 11.187502] rtl9010_power_on:GPIO_PHY_VSYS request. [ 11.187506] rtl9010_power_on:GPIO_PHY_POWER request . [ 11.187510] rtl9010_power_on:GPIO_PHY_RESET request . [ 11.266424] rtl9010_hardware_reset success! [ 11.270827] RTL9010Ax_Initial_Configuration: RTL9010 ============ [ 11.281850] RTL9010Ax_Initial_Configuration_Check: RTL9010 ============ [ 11.293280] RTL9010Ax_Initial_with_SGMII_Configuration: RTL9010 ============ [ 11.330971] RTL9010Ax_Initial_with_SGMII_Configuration_Check: RTL9010 ============ [ 11.394608] RTL9010Ax_Soft_Reset: RTL9010 ============ [ 11.401536] am65-cpsw-nuss c000000.ethernet eth0: Link is Up - 1Gbps/Full - flow control off [ 11.988494] ipv6: Unknown symbol make_kuid (err -2) [ 11.994075] ipv6: Unknown symbol __put_net (err -2) [ 11.999591] ipv6: Unknown symbol from_kuid_munged (err -2) [ 12.962492] k3_r5_rproc bus@100000:r5fss@5e00000: Timed out waiting for 5e00000.r5f core to power up! [ 19.884890] kauditd_printk_skb: 8 callbacks suppressed [ 19.884897] audit: type=1006 audit(1709134540.728:16): pid=834 uid=0 old-auid=4294967295 auid=0 tty=(none) old-ses=4294967295 ses=3 res=1 [ 19.902858] audit: type=1300 audit(1709134540.728:16): arch=c00000b7 syscall=64 success=yes exit=1 a0=8 a1=fffff83be848 a2=1 a3=1 items=0 ppid=1 pid=834 auid=0 uid=0 gid=0 euid=0 suid=0 fsuid=0 egid=0 sgid=0 fsgid=0 tty=(none) ses=3 comm="(systemd)" exe="/usr/lib/systemd/systemd-executor" key=(null) [ 19.929916] audit: type=1327 audit(1709134540.728:16): proctitle="(systemd)" [ 19.937187] audit: type=1334 audit(1709134540.732:17): prog-id=18 op=LOAD [ 19.944308] audit: type=1300 audit(1709134540.732:17): arch=c00000b7 syscall=280 success=yes exit=8 a0=5 a1=ffffc0f4c738 a2=90 a3=0 items=0 ppid=1 pid=834 auid=0 uid=0 gid=0 euid=0 suid=0 fsuid=0 egid=0 sgid=0 fsgid=0 tty=(none) ses=3 comm="systemd" exe="/usr/lib/systemd/systemd" key=(null) [ 19.970203] audit: type=1327 audit(1709134540.732:17): proctitle="(systemd)" [ 19.977454] audit: type=1334 audit(1709134540.748:18): prog-id=18 op=UNLOAD [ 19.984645] audit: type=1300 audit(1709134540.748:18): arch=c00000b7 syscall=57 success=yes exit=0 a0=8 a1=1 a2=0 a3=ffffb21fec60 items=0 ppid=1 pid=834 auid=0 uid=0 gid=0 euid=0 suid=0 fsuid=0 egid=0 sgid=0 fsgid=0 tty=(none) ses=3 comm="systemd" exe="/usr/lib/systemd/systemd" key=(null) [ 20.010329] audit: type=1327 audit(1709134540.748:18): proctitle="(systemd)" [ 20.017505] audit: type=1334 audit(1709134540.748:19): prog-id=19 op=LOAD [ 23.170984] platform 2701000.can: deferred probe pending [ 23.176297] platform 2920000.pcie: deferred probe pending [ 23.181690] platform 2900000.pcie: deferred probe pending [ 23.188266] platform 2910000.pcie: deferred probe pending [ 23.193680] platform can-phy2: deferred probe pending [ 52.009580] ipv6: Unknown symbol make_kuid (err -2) [ 52.014695] ipv6: Unknown symbol __put_net (err -2) [ 52.019685] ipv6: Unknown symbol from_kuid_munged (err -2)