Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

Team,

I was looking at the below post:

https://e2e.ti.com/support/processors-group/processors/f/processors-forum/1552878/tda4vh-q1-how-should-i-troubleshoot-a-link-up-failure-issue

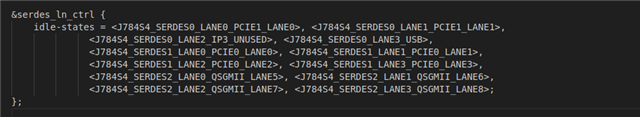

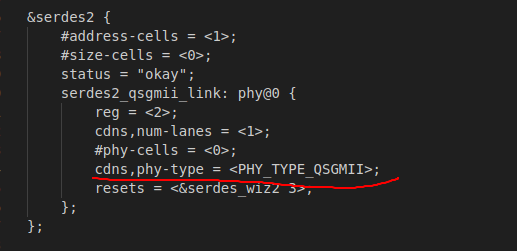

that talks about configuring the same SERDES for two protocols.

There is the below comment in the E2E post:

'PCIe + SGMII (1Gbps) -> Supported from TI Linux SDK. Need to configure from the boot loader i.e., U-boot.'

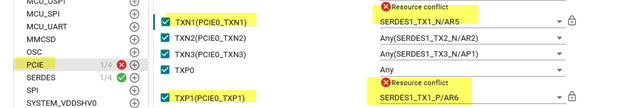

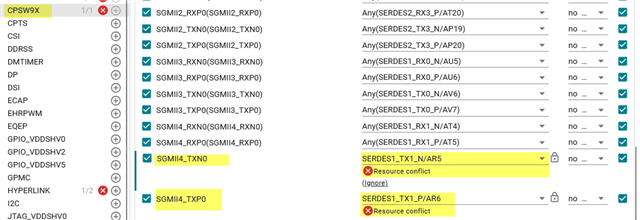

-How should the pinmux setup in sysconfig look like?

The setup for CPSW9x and PCIe module in sysconfig for the same SERDES pin does shows a pin conflict.

PCIE / PCIE0_TXP1 signal -> SERDES1_TX1_P/AR6 pin

CPSW9x / SGMII4_TXP0 signal -> SERDES1_TX1_P/AR6 pin

but I guess it is correct in case two protocols are being used on the same SERDES?

-What are you general advises when doing the pinmux config for SERDES for both sinle protocol and dual protocol in sysconfig?

- Only the Signal (like SGMII4_TXP0) to pin (SERDES1_TX1_P/AR6 pin) assignment can be done in sysconfig. Correct?

The specific Mode (2.5Gb SGMII/XAUI, 5Gb QSGMII, ..etc) has to be done by SW. Correct?

Sysconfig:

Thanks in advance,

Anthony