Other Parts Discussed in Thread: PROCESSOR-SDK-J721S2, TDA4VL-Q1, TDA4VM

Tool/software:

Hi

Our PROCESSOR-SDK-J721S2 version is pdk_j721s2_10_01_00_25

.Symptom:

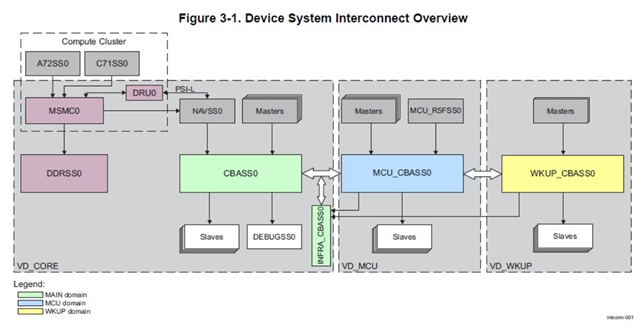

Under heavy Camera/Perception loading on MAIN domain (A72/C7x/R5F), MCU_R5F (MCU1_0) shows jitter and higher CPU loading.

.What we tried:

Moved Deterministic code/data to MSMC/OCMC/TCM → but our all MCU code is too big , some MCU code still needs in DDR.

.Request:

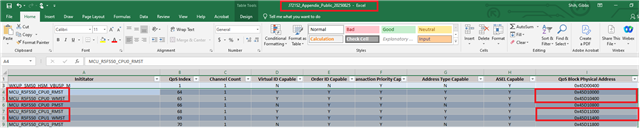

Please provide the patch to Raise MCU R5F DDR access priority on pdk_j721s2_10_01_00_25.

Note: we understand QoS improves priority but does not guarantee bandwidth; goal is to minimize jitter while heavy Camera/Perception loading on MAIN domain

B.R.

Sanhsin Kuo