Part Number: AM69

Tool/software:

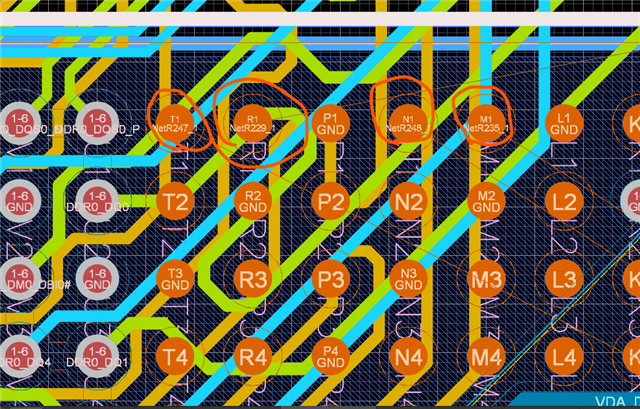

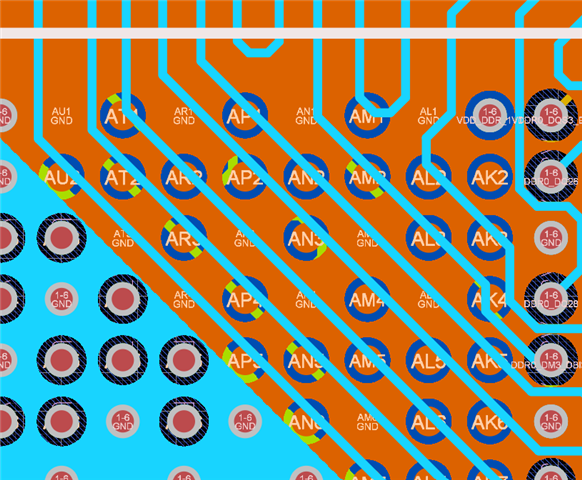

I'm in need to connect certain pads to VSS/GND to make a complete solid reference plane at the top because second layer is used as high speed signal.

I know that you should not connect certain pads/balls of the processor directly to VSS/GND because it can cause current rush. Therfore, it's recommended to add a pull-down resistor instead to protect the IO.

According to " 5.4 Pin Connectivity Requirements" from the datasheet of AM69 processor. There we can find the following:

- Some pins must be connected directly to an arbitary pull-down to VSS/GND, if unused.

- Some pins must be connected directly to an approprite pull-down to VSS/GND, if unused.

- Some pins can be connected directly to VSS/GND, if unused.

- Some pins must be connected directly to an arbitary pull-up to specific VCC, if unused.

But what if I just remove the power? First of all, I don't need DDR1 to DDR3. Why not remove the 0-ohm resistor that enables the current flow to the processor for DDR1 to DDR3? I only need DDR0.

Same as some of the serdes, all of CSI, DSI and MMC0. I'm only need MMC1 due to the SD-card.

So what would happen if I "unplug" the power to specific peripherals of AM69?

- Will the processor still boot?

- Will the pins have no voltage? E.g they are like...no connected to anything?

- Will it disable the peripheral and no issue will occur?

The reason why I'm asking this question it's because I have not find any information how to disable peripherals at the initial start of the processor. The goal is to connect the whole DDR1 directly to VSS/GND if it's not used.

See the reference schematic SK-AM69 for the PDN.