Tool/software:

Dear TI Support Team,

I am working with the TI TDA4 J784S4 SoC and referring to the attached SPRUJ52D Technical Reference Manual (TRM). I need clarification on the interaction between the A72 core, the R5F firmware, and the CPSW9G switch, specifically regarding access to the CPTS (Common Platform Time Sync) module for timestamping.

From the TRM, I understand that:

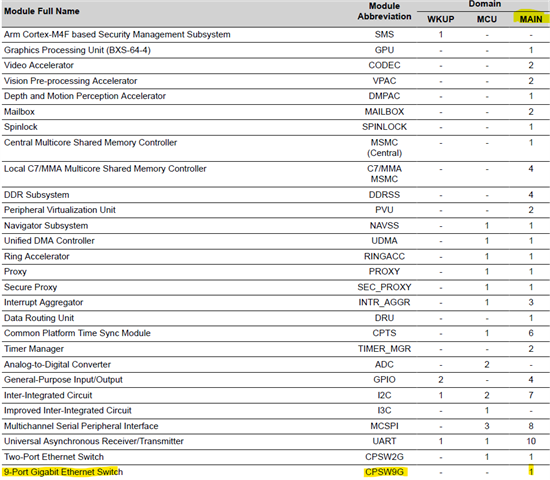

- CPSW9G is part of the MAIN domain as mentioned in this table at section 1.1.3.

- Section 12.2.2.1.1 confirms that CPTS is a part of the CPSW9 switch.

- CPTS is designed to supports both software and hardware timestamping and provides mechanisms for precise time tracking and synchronization across various subsystems. I’m particularly focused on the CPTS functionality within the CPSW9 switch, as my development scope involves creating a kernel driver for VxWorks that runs on the A72 core and performs diagnostic testing related to the CPTS registers in CPSW9.

Could you please clarify:

- How does the A72 core communicate with the R5F firmware to configure or retrieve timestamps from the CPSW9G CPTS module?

- Can the A72 core directly access CPTS registers, or does it require coordination with R5F firmware?

- Is there a standard mechanism or protocol (e.g., mailbox, shared memory, interconnect) used for this communication?

- Are there specific TRM sections or examples that detail this interaction?

Any guidance or references to TRM pages or SDK examples would be greatly appreciated.

Best regards,

Akhil M Nair

5315.SPRUJ52 - J84S4 AM69A TRM.pdf