Part Number: AM62L

Other Parts Discussed in Thread: TMDS62LEVM, UNIFLASH

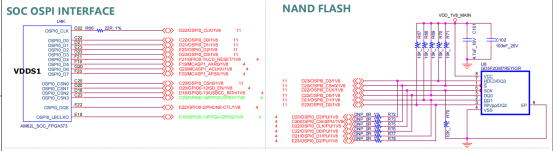

Hello, expert. Currently, we are testing the QSPI FLASH boot of AM62L32. The following is our schematic design

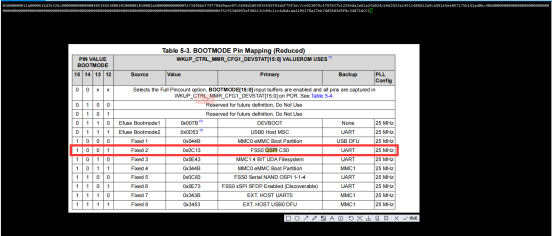

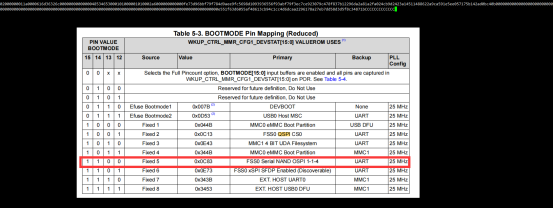

Whether we use FSS0 QSPI CS0 or FSS0 Serial NAND OSPI 1-1-4 mode, we cannot boot normally. The specific log is as follows; But it can read and write QSPI FLASH normally. May I ask what the reason is?