Part Number: AM623

Other Parts Discussed in Thread: SYSCONFIG, AM625SIP, AM625-Q1, AM625, AM620-Q1, AM62D-Q1, SK-AM62B-P1, SK-AM62-LP, SK-AM62B, SK-AM62-SIP

We have designed a custom board based on the AM623 that we are having trouble getting past getting the processor out of reset (RESETSTAT_N never is pulled up) so it seems likely we've made a mistake somewhere in the hardware. Our schematic is loosely based on the PROC162E1 where we are using the TPS6521904 as the primary PMIC. We believe we are following the required power up sequencing but have the following concerns:

- 3.3V is supplied externally from the board so from the board's perspective VSYS == VDD_3V3. Would this be a problem?

- VSYS_MON is tied directly to ground as we are not using it as recommended by the datasheet. This seems to contradict the power up sequencing diagram in the datasheet which depicts that signal rising. Is this required to be powered to get the system out of reset?

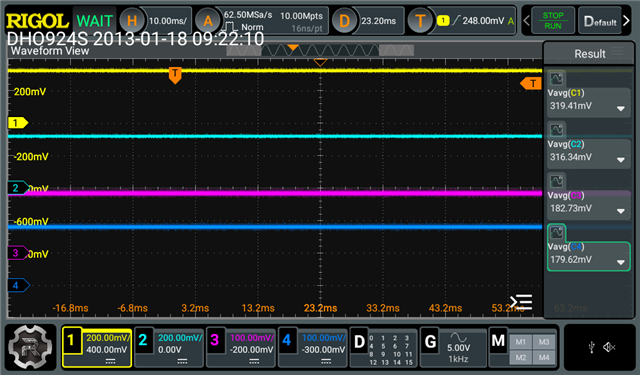

Below are captures of our power up sequence:

Yellow: VDD_3V3

Light Blue: VDD_1V8

Purple: VDD_DDR

Dark Blue: VDD_CORE

Same trigger but other scope:

Yellow: VDD_3V3

Light Blue: VDD_SD

Purple: VDDA_1V8

Dark Blue: POR_Z

Not pictured is the 25MHz LVCMOS that we have confirmed to be oscillating on startup with VDDA_1V8.

The PORZ signal is currently being controlled by an onboard MCU that monitors voltage stability and inserts a 20-30ms delay before pulling PORZ up.

Schematics and PCB are available upon private request.