Hello.

I am working on DM8168 evm board with EZSDK 5.03.01.15.

I want to use C6EZAccel library (2.01.00.10) with video input and output.

But as mentioned in the document (http://processors.wiki.ti.com/index.php/DM816x_C6A816x_AM389x_EZ_5.02_Software_Developers_Guide#Running_the_C6Accel_apps),

the C6Accel apps should not be run out with graphics like other syslink or codec engine examples.

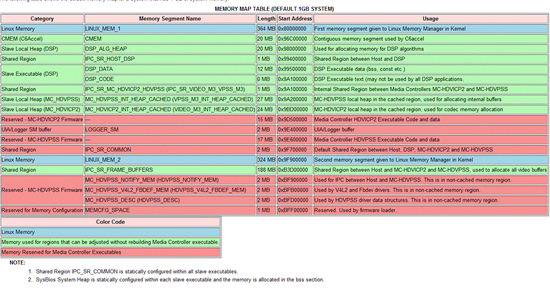

So I cannot run the sample application with default VPSS and HDVICP2 firmwares are loaded using syslink.

When I try to run C6Accel apps with those drivers loaded,

assert message is printed and the app is hanged like below.

root@dm816x-evm:~/c6accel_dsplib_testapp# ./c6accel_dsplib_testapp

******************************************************************************

Sample application for testing kernels in C6Accel started.

******************************************************************************

CERuntime complete

Assertion at Line no: 301 in /swcoe/sdk/cm/netra/arago-tmp/work/dm816x-evm-none-linux-gnueabi/ti-syslink-2_00_05_85-r4i/syslink_2_00_05_85/packages/ti/syslink/utils/hlos/knl/Linux/../../../../../../ti/syslink/ipc/hlos/knl/Linux/IpcDrv.c: (status >= 0) : failed

To run the application I have to unload drivers.

# /etc/init.d/load-hd-firmware.sh stop

But this environment is not what I want because I have to use video input and output drivers.

What should I do, if I want to run c6accel app or DSP codec engine app with VPSS and HDVICP2 firmwares and drivers loaded?

Regards,

Juho