Hi all,

I need a example of timer (in watchdog mode is better) on evm6678. I searched pdk for it,but it seems haven`t.

Do you have some example?I need it.

Thanks.

Li

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi all,

I need a example of timer (in watchdog mode is better) on evm6678. I searched pdk for it,but it seems haven`t.

Do you have some example?I need it.

Thanks.

Li

There's one in the PDK.

C:\ti\pdk_C6678_x_x_x_x\packages\ti\csl\example\timer

Best Regards,

Chad

Hi Chad,

I tired to use the .c file and cmd, but my new project is not work, maybe I config is wrong when i create it.

Can you help me for create a new usable test project with the two file?

Thanks,

Li

Not sure what the issue is w/o seeing the compiler outputs.

The .cmd file in the directory looks fine.

Looking at the code, the pathing for the include files look fine, but you'd need to have the include path in the project to get to the STDIO and the PDK Package so it will get these headers.

#include <stdio.h>

#include <string.h>

#include <ti/csl/csl_tmr.h>

#include <ti/csl/csl_tmrAux.h>

#include <ti/csl/src/intc/csl_intc.h>

#include <ti/csl/src/intc/csl_intcAux.h>

Best Regards,

Chad

Hi chad,

I have tried it like you said, but it did`t work,

compiler told me some Fxn undefined (like IntcOpen IntcClose etc),

but i have included these header file and set search path,even add 66lib

so i`m confuse...

Can you try it? Thanks.

Best Regards,

LI

I'll have someone from my team try and and get back to you on the forum.

Best Regards,

Chad

HI Li,

I can see you're having some problems and am happy to help. From what I can tell in your CCS setup is that you have your path included in your C6000 linker and compiler (which you can see in detail from your CCS project preferences). Since you said you have your header files and search path set correctly, what you're probably missing is the library for the intc (interrupt controller) function definition. You should need two libraries for this example.

So, if I am using the ti.csl.ae66 library (C:\ti\pdk_C6678_xxx\packages\ti\csl\lib) , I also need the ti.csl.intc.ae66 library included as well. You can include this in the "File Search Path" portion of CCS project preferences. It will be under "C6000 Linker".

I hope this solves this problem for you. If you have any other questions feel free to ask again!

Regards,

Kat Kelsch

HI Kat,

Thank you for your answer.It is right.I used the two library and then the problem resolved.

I want to use the timer watchdog mode.

I have two question for the code:

Q1:

in this Function static Int32 test_wd_timer (Uint8 IntcInstance)

/* Wait for the timer interrupts to fire; since the watchdog timers run continuously

* we wait for at least 5 interrupts to fire... */

while (timerISRCounter != 5);

I only get timerISRCounter =1 in watchwindow(called Expressions in v3.3),and wait for ever.

I think When the wd send a interrupt.It will be disable.so the timerISRCounter =1.It`s right?

Why the code is 5?

Q2:the register CNTLO and CNTHI at 0x02200010 and 0x02200014, i think it wil add 1 by 1.But it still remain 0.Why?

Thanks,

Li

Hi kat

I saw TIMER64P_UG.paf .

It said After entering the timeout state,the watchdog timer cannot be enabled again until a hardware reset occurs.

is it the one reason of My question?

I think the chip will reset and the project will be disconnect, is it right?

Thanks,

Li

Li,

You can perform a Soft Reset, please see the Data Manual for details. This will not disconnect the emulation and it will not invalidate the memory.

Best Regards,

Chad

Hi Li,

Let's do this question by question.

Q1: Once the device is stuck in timeout state, you will need to do a hardware reset in order to enable the timer. You're correct about that. You will terminate the CCS session (you can just click the red square in your CCS debug session) and it will disconnect the project. You won't hardware reset until you turn your EVM on and off or press the reset button. Then you can relaunch your debug session and start over. Your other option is of course the soft reset, as Chad said.

You're also correct in that the timer is stuck waiting for the other interrupts to happen. This means that there is something wrong with your setup that would cause the interrupts to not communicate. Check and see if you can find what that is.

Q2: You're right, those two registers should increase 1 by 1. However, since the system gets stuck before hand at the interrupt. It will never be able to increase since it is paused before it gets to that point in the code.

Regards,

Kat Kelsch

Hi kat,

Thanks for your reply seriously.

I`m sure my config is right as sprugv5a_KeyStone_Arch_TIMER64P_UG.pdf said.

watchdog mode,PLUS mode,PLUS wide = 3 or 4,no gated clock,no external clock,no one-time enabling etc.

It seems the problem of watchdog proccess.

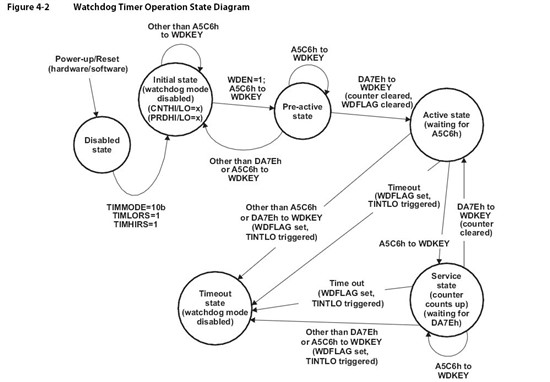

Q1:In initial statue, I enable the wd and key A5C6h to WDKEY,we are into pre-active state.That is right.

And then,the problem is occured.

Write DA7Eh to WDKEY.it should into Active state(In the state, we are waiting for A5C6h).

That means the counter still remain 0 if I didn`t write A5C6h to WDKEY. I`m right?

The fact is when I have write A5C6h and DA7Eh first time.(It should into Active state and wait A5C6h)

But it start counting. It make me confused.

Q2:I think the watchdog timer can realize hard reset, soft reset and,local reset.as the following image

Q3:I think I can answer the reason of I get only one interrupt.

Because when the timeout occuerd, the WDFLG is set 1 and WDEN is 0,

and I think the watchdog can`t enable again if no hard reset happened.

I think the change between Active state from Service state,it can be called kick dog.

I`m so embarrassed,because i just leave university to working only three months,

so I told something maybe wrong,Please tell me directly.Thanks.

Li

Hi Chad,

I feel confuse about how to make timer-watchdog mode realize soft reset / hard reset / Local reset.

The Manual describe the different of these.

But I feel it is not detailed about realize them.

And For example,If i want to use soft reset,I must set 1 at WDTYPE[N] in RSTCFG (PLL register),

I have tried it,but the bit can`t be written like only read,though it is R/W.

The code about interrupt like this:

/* Open INTC */

vectId = CSL_INTC_VECTID_12;

tmrIntcHandle = CSL_intcOpen(&tmrIntcObj, CSL_GEM_TINTLN, &vectId, NULL);

if (tmrIntcHandle == NULL)

return -1;

/* Bind ISR to Interrupt */

EventRecord.handler = (CSL_IntcEventHandler)&WatchDogTimerHandler;

EventRecord.arg = (void *)CSL_GEM_TINTLN;

CSL_intcPlugEventHandler(tmrIntcHandle, &EventRecord);

/* Event Enable */

CSL_intcHwControl(tmrIntcHandle, CSL_INTC_CMD_EVTENABLE, NULL);

Best Regards,

Li

Hi Li,

Q1: You're right, it should not start couting until it receives the watchdog key "A5C6h". You said "That fact is when I have write A5C6h and DA7EH", if you did write those, it should start counting, if you did not write those, it should remain 0 and go into the Time Out state. However, you may have accidently written to it the A5C6h value it needs.

Q2: For your purposes any of the resets would work, but you may prefer some over the others since you won't have to reconnect to CCS and power down your device.

Q3: Don't feel embarrassed. This term to alert the watch dog is commonly called "kick the dog" or "wake up the dog" and other terms. It is clear that you are only getting one interrupt and the code is waiting for 5. The reason the code does not get another interrupt is that the WDEN (watch dog enabled) is 0, or disabled. So the other 4 interrupts are not sent. It cannot be enabled again until a reset.

Kat.

Hi Kat,

Tanks for your reply.

Q1:About the Q1, I said"That fact is when I have write A5C6h and DA7EH at first time ", it means if the process of the State Diagram is correct,

it should still remain 0 at Active statue,and wait my key"A5C6h",But now it is counting.

I note From Active statue to Timeout state have a timeout process,

so I doubt when WD into Active statue,it counting immediately. Because if it is not like i said, WD How to know when the timeout occurred.

Q2:Today, I use SWRST at PLL RSTCTRL register, implement software reset in my WD interrupt routine. It looks like system reset of CCS.

But use WDTYPE at PLL RSTCFG register is not work.

And i think implement any reset can depend on timer output pin,not only interrupt. I`m not sure the output pin have connected to RESET pin?

Q3:Have you run the example (pdk_C6678_x_x_x_x\packages\ti\csl\example\timer)?the Function about WD is work well(into 5 times interrupt routine)?

I think it maybe can`t pass the test . Because if WD into time statue, it will be disable until a hardware reset (like Power on level reset)occurs.so how to into

interrupt 5 times?

Q4:Do you have some example about soft/hard/local reset? Or Anybody have do this from your team?

I have search many times in E2E,but no body do this on EVM6678.

I feel i implement the soft reset way which is not TI design way, and have no idea about this.

Thanks,

Li

Hi Chad,

I have implement Soft Reset by set SWRST in RSTCTRL register of PLL. is it your way to implement Soft Reset?

I think is not TI design way to use watchdog implement Soft Reset.And i want to implement soft/hard/local reset such timer manual said.

But now have no idea bout this, have you any idea?or example from your team?

And the most important is the example about timer from pdk 6678, Are you sure the example can work well(about watchdog function can pass test)?

Thanks,

Li

Hi Li,

Q1: Li, I think once you write both A5C6H and DA7EH, the watch dog will count. In state one of that diagram in order to go into state 2 (inital state watchdog mode) and then into state 3 (Pre -active state) you have to have WDKEY = A5c6h. In order to go into state 4 (Active State) you have to have DA7eh. I think what is happening is that in your code you have the EVM or device or your 6678 chip responding with the A5C6H. So it is telling the code to continue to kick or wake the dog.

Q2: I don't understand what you're asking here exactly, but different reset types can be done on board with a button or in software like you did via CCS. (You can get more information about this in the 6678 user guide on page 127 and page 139 at http://www.ti.com/lit/ds/symlink/tms320c6678.pdf ) Toggling back and forth the WDTYPE in the RSTCFG from 0 to 1 or 1 to 0 should cause the hard reset or soft reset you need based on how you programed the 12 bit for Reset type in RSTCFG. I know this is probably an obvious question, but you are connecting back the EVM and doing the basic configurations between resets, correct?

Q3: Yes, this example like all of TI example packages goes through a check and correct process to make sure it is valid and working well for customers. I can assure you it has worked here at TI and for other TI device users.

Q4: Since soft/local/hard resets are such a basic feature for every chip and device that TI produces, there isn't an example for purely that. Every TI engineer has done this process since it is cruical for JTAG debugging. I suggest looking at the EVM page (http://processors.wiki.ti.com/index.php/TMDXEVM6678L_EVM_Hardware_Setup). There are hardware buttons ON the board that you can reset the system with and software methods as you did before. Both are considered TI approved ways to reset the system for the device, respectively. There is also the EVM specific EVM refence manual that may be helpful to you as well (http://www.advantech.com/Support/TI-EVM/6678le_sd.aspx ) and a getting started guide. These should have some more answers as far as resets.

Here are a couple of e2e forum answers that may interest you as well:

http://e2e.ti.com/support/dsp/c6000_multi-core_dsps/f/639/t/193265.aspx

http://e2e.ti.com/support/dsp/c6000_multi-core_dsps/f/639/t/187102.aspx

http://e2e.ti.com/support/dsp/c6000_multi-core_dsps/f/639/t/187175.aspx

Thanks,

Kat

Hi Kat,

Thanks for your reply.

Today is my lucky day, I have finish the work,implement the three kinds reset.

I have to test them next in the following days for my team.

In this work, I found some error on the example and User`s Guide.I will post them for you, when

I have make sure them.My English is not very well,so you maybe feel confuse for my said.

I recently use 6678. so Keep in touch.Thank you very much.

Best Regards,

Li

Hi Li,

I am trying to perform Hard Reset using watchdog timer but i can't see what i am doing wrong. I can see WDFLAG was getting set once timeout occur on watchdog timer. My reset control register is correctly set to perform HARD RESET on WDTYPE (set to 0) but Hard reset never occurs.

I can see you have found error in manual and TI example code. Can you please send me those details?

Kind Regards,

Piyush N. Prince

Hi Piyush,

TI example:..\ti\pdk_C6678_1_1_2_5\packages\ti\csl\example\timer, I use it setup timer.

Some error about procedure as I said before. But I think it can`t make Hard reset become invalid.

As the image, You can know many ways to perform Hard Reset. We can use PLLCTL perform HR in WD timeout interrupt routine.

I have try what you do.But actually it seems can`t work.So I use PLLCTL.It`s looks very well. :D

Best Regards,

Li

Hi Li,

I can perform PLL reset but not automatically using watchdog. Thanks you for your help.

I will raise this with TI and try to get some answerd in terms of why Watchdog timeout does not reset the chip.

Kind Regards,

Piyush