Dear All,

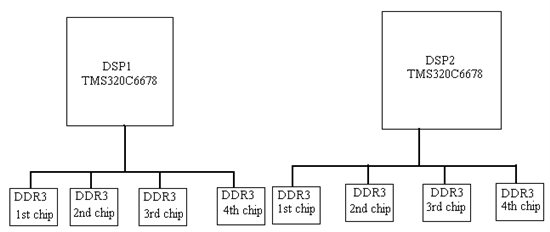

We were currently working on C6678. In the customer Board there were two C6678 processor. 1GB DDR3 is connected C6678 (We want to implement a 64 bit interface based on x16 bit DDR3 chips, therefore requiring 4 devices).

The routing length between the DSP1 and DDR3 , DQS signal Length = 1547 and DDR clock signal length = 5156.

The routing length between the DSP2 and DDR3 , DQS signal Length = 1747 and DDR clock signal length = 5156.

I can able to access the 64-bit of the DSP1 and DDR3. But in the DSP2 and DDR3, I can't able to 16-bit of the DDR3(particularly 3rd DDR3 chip). In the GEL ,the file Partial Automatic Leveling is implemented.

I have tried with Fixed Leveling, but the issue doesn't solved. After trying the Fixed Leveling, I immediately tried with Partial Automatic Leveling . I can able to access the 64-bit for few seconds. After few seconds I can't able to access the 16-bit once again.

I have also attached the model and Gel file along with this mail.

I have also probed the 3rd DDR3 chip. The Chip is working as like of the other chips.

Questions:

1. How to calculate the strip line Delay per inch?

2. What is the need of Invert Clock. It is must required?

3. Will there any issue due to DQS routing difference? Because for 1'st DSP it works perfectly, Not for the 2'nd DSP

Regards,

Avinash N