hello,I‘m using 6678EVM to communicate with Xilinx K7 platform ,now I have some problem as follow,

description:

test platform : 6678EVM and Xilinx K7

test code :the SRIO test code for 6678 is downloaded from TI chinese forum "http://www.deyisupport.com/",and the test code for K7 is generated from IP CORE

question :

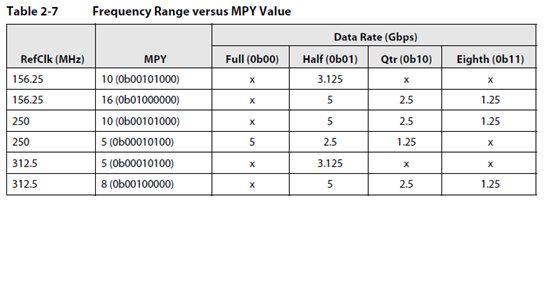

1.The SRIO speed is set to 5Gbps,and the reference clock for SRIO on 6678 is 312.5MHz, while it is 125MHz on Xilinx K7,does it matter that they doesn't equal?

2.In my test ,the DSP is slave ,and FPGA is master, when I run the program on dsp,I see a print message which is "the dsp is ready for test",but how can I make sure that it has been woring right.

3.When I readthe code for DSP ,In digital loopback mode, I see the DSP is configured as processor,but I tried to change it to memory and bridge ,it also works right(because I see the print message show that the test is complete ),does it any difference among processor ,memory,switch and bridge; In my opinion,you should configure this parameter by the type of the SRIO device ,so the 6678 can only be configured as processor ,otherwise, it surely doesn't work, and I think a SRIO device which is configured as memory can't issue any request ,it can only receive request , does my comprehension right, waiting for your answer,thank you!