Hi,all:

Now I do a work about port a SRIO software example(http://e2e.ti.com/cfs-file.ashx/__key/communityserver-discussions-components-files/639/2677.K1_5F00_STK.7z) which

worked well on EVMC6678 to the platform DSPC-8681E with four C6678s.

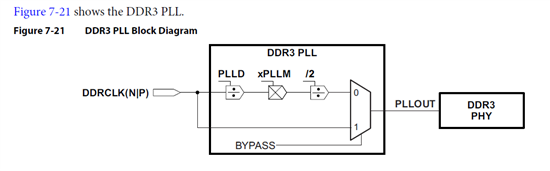

The key point is about DDR3 config or init.

And the difference between EVMC6678 and DSPC-8681E is frequence of input

refclk.

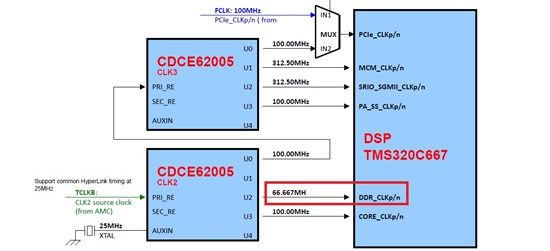

On C6678EVM DDR input refclk is 66.667MHZ(learned from 5852.TMDSEVM6678L_Technical_Reference_Manual_2V01_0320.pdf):

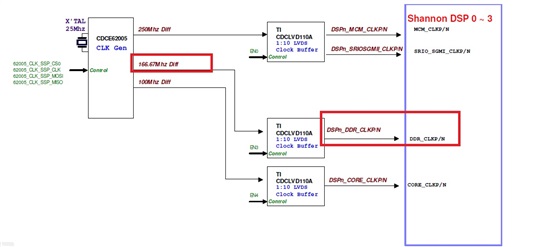

On DSPC-8681E DDR input refclk is 166.67MHZ(learned from 6131.DSPC-8681E HW User Manyal_V0.3_20120621.pdf):

Meanwhile,the source code of C6678EVM DDR init in SRIO example is below:

//DDR init 66.66667*20/1= 1333

KeyStone_DDR_init (66.66667, 20, 1, NULL);

In the above statement, 66.66667 is the DDR input refclk frequence.PLLM = 20,

and PLLD is 1.1333 is the work frequence of DDR3 which is on EVMC6678.So,If you

want to get 1333MHZ,you must calc like this:66.66667*20/1= 1333. So,you get PLLM

=20,PLLD = 1.But Is PLLM = 40 PLLD = 2 ok?And Are others value ok only if the value

of PLLM/PLLD is 20? I think so.Isn't wright?

So,According to my guess above.When I port the source code from EVMc6678 to DSPC8681E.

I modify the source code about DDR init like below:

KeyStone_DDR_init (166.67, 8, 1, NULL);

Because 166.67*8/1 = 1333.36MHZ. So I set those values like above.

But,when I run that code on DSPC8681E board. I cannot pass the memory test of DDR.

I find that the value which I read from the DDR in some address is not the value that

I write into the same address of DDR.

Since,I don't know where I make mistake? How can I config DDR3 registers on DSPC-8681E

considering that its DDR input refclk is 166.67MHZ not 66.667MHZ and the target frequence

of DDR3 on DSPC-8681E is 1333MHZ?

Kindly Regards!

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.