Other Parts Discussed in Thread: TMDSEVM6657

hi,

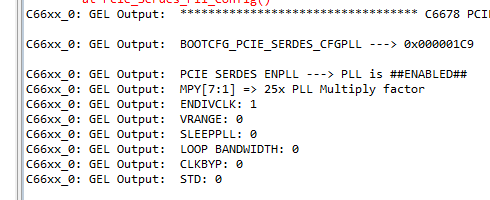

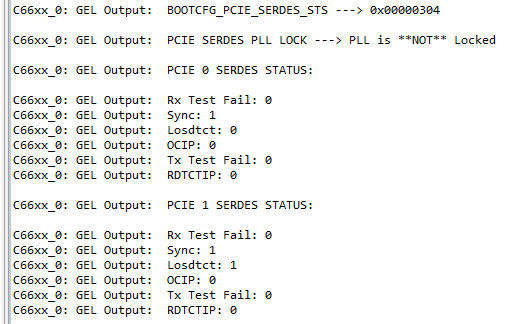

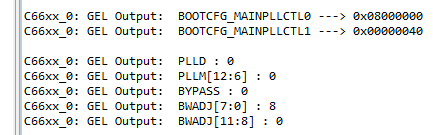

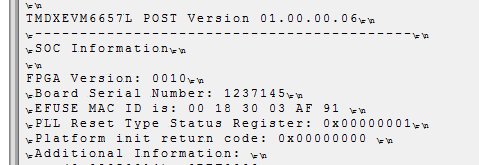

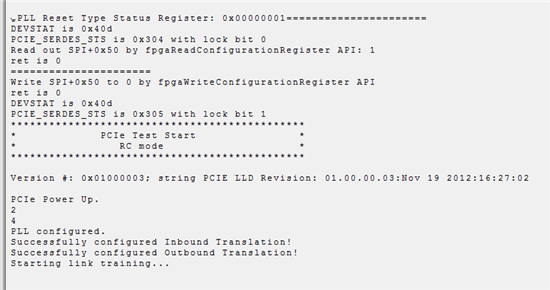

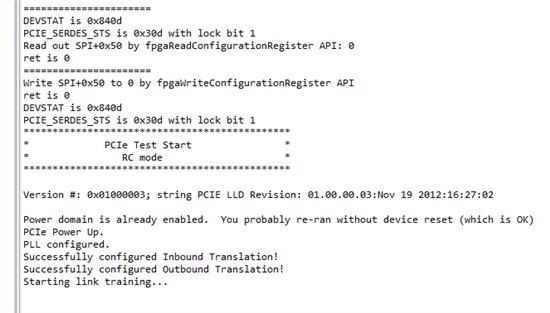

I found out that PCIE_exampleProject just works fine (successful communication between EP and RC), when I boot the DSP via I2C POST boot in advance.

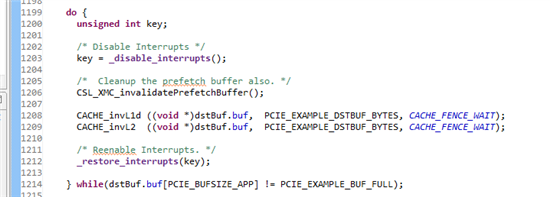

When I choose "no boot" or "ROM SPI boot" and load the PCIE_exampleProject.out afterwards the code will never leave

while (!lock)

{

CSL_BootCfgGetPCIEPLLLock(&lock);

}

. Even when I load the post_evmc6657l projects before to execute the booting process by hand I will have the same problem.

Any idea what part is missing to run the PCIE_exampleProject without booting in POST mode?

Regards, Gregor