Hi all,

I try to find why delay between two successive read accesses is fixed at 180ns when GPMC clock at about 120 MHz and successive delay at gmpc GPMC_CONFIG6_i is set to 0.

The parameter setting for gpmc is bellow:

GPMC_CONFIG_xy 0x6E000050

bit1:0 for no Limited Address device

GPMC_CONFIG1_4 0x6E000060 + (0x00000030 * 4)

bit30:0x0 READMULTIPLE for Single Access

bit29:0x1 READTYPE for Read Asynchronous

bit26~25:0x0 CLKACTIVATIONTIME for First rising edge of GPMC_CLK at start access time

bit24~23:0x0 ATTACHEDDEVICEPAGE LENGTH for 4 Words

bit22:0x0 WAITREADMONITORING for Wait pin is not monitored for read accesses

bit13~12:0x1 DEVICESIZE for 16 bit

bit11~10:0x0 DEVICETYPE for NOR Flash like, asynchronous and synchronous devices

bit9:0x1 MUXADDDATA for Address and data multiplexed attached device

bit4:0x0 TIMEPARAGRANULARITY for x1 latencies

bit1~0:0x0 GPMCFCLKDIVIDER for GPMC_CLK frequency = GPMC_FCLK frequency

GPMC_CONFIG2_4 0x6E000064 + (0x00000030 * 4)

bit12~8:0x7 CSRDOFFTIME for 7 GPMC_FCLK cycle

bit7:0x0 CSEXTRADELAY for CS I Timing control signal is not delayed

bit3~0:0x1 CSONTIME for 1 GPMC_FCLK cycle

GPMC_CONFIG3_4 0x6E000068 + (0x00000030 * 4)

bit12~8:0x5 ADVRDOFFTIME for 5 GPMC_FCLK cycle

bit7:0x0 ADVEXTRADELAY for CS I Timing control signal is not delayed

bit3~0:0x2 ADVRDOFFTIME for 2 GPMC_FCLK cycle

GPMC_CONFIG4_4 0x6E00006C + (0x00000030 * 4)

bit12~8:0x7 OEOFFTIME for 7 GPMC_FCLK cycle

bit7:0x0 OEEXTRADELAY for CS I Timing control signal is not delayed

bit3~0:0x4 OEONTIME for 4 GPMC_FCLK cycle

GPMC_CONFIG5_4 0x6E000070 + (0x00000030 * 4)

bit27~24:0x1 PAGEBURSTACCESSTIME for 1 GPMC_FCLK cycle

bit20~16:0x5 RDACCESSTIME for 5 GPMC_FCLK cycle

bit4~0:0x7 RDCYCLETIME for 7 GPMC_FCLK cycle

GPMC_CONFIG6_4 0x6E000074 + (0x00000030 * 4)

bit11~8:0x0 CYCLE2CYCLEDELAY for 0 GPMC_FCLK cycle

bit7:0x0 CYCLE2CYCLESAMECSEN for No delay between the two accesses

bit6:0x0 CYCLE2CYCLEDIFFCSEN for No delay between the two accesses

bit3~0:0x2 BUSTURNAROUND for 2 GPMC_FCLK cycles

GPMC_CONFIG7_4 0x6E000078 + (0x00000030 * 4)

bit6:0x1 CSVALID for CS enabled

CONTROL_PADCONF_GPMC_NCS7 0x480020BC

bit24:0x1 INPUTENABLE1 for looped-back GMPC_CLK requirement at section 11.1.3.2.1

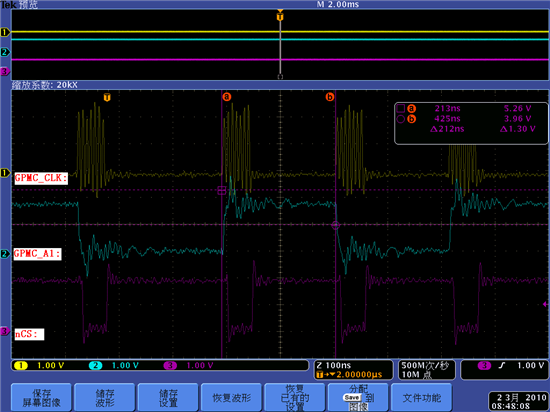

From figure, The time delay between a and b is fixed.

I want to reduce the delay. But even though I set the read cycle 3 clock, the gpmc clock nums is reduced according to my setting , the delay between is remain.

It seems that the delay between is left for max burst word clock, so if you don't use burst. The delay is still left for no use.

Is there any suggestion for me?