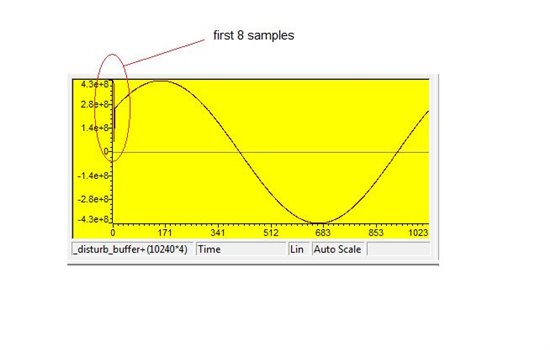

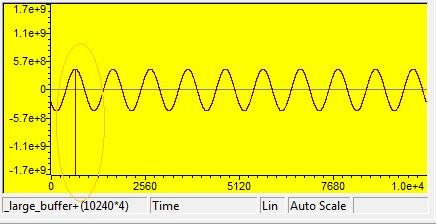

I set EDMA3 LLD 01_11_00_03 in order to transfer 8 McASP channels to SDRAM external memory using double (ping-pong) buffering. When acquisition is completed an EDMA3 chaining starts a transfer to sort samples in another 8 SDRAM buffers. And when final TCC is completed I immediately copy the final 8 buffers to another 8 ones for data integrity checking. Next there is a capture of one of the 8 buffers.

The same disturbance appears at the first 8 samples of 8 buffers in every acquisition. I guess this is due to some memory stall but I'm not sure. How could I check or debug this issue? Thanks in advance,

gaston