Hi. Info from the Release Notes - I'm using MCSDK Release 3.0.3.

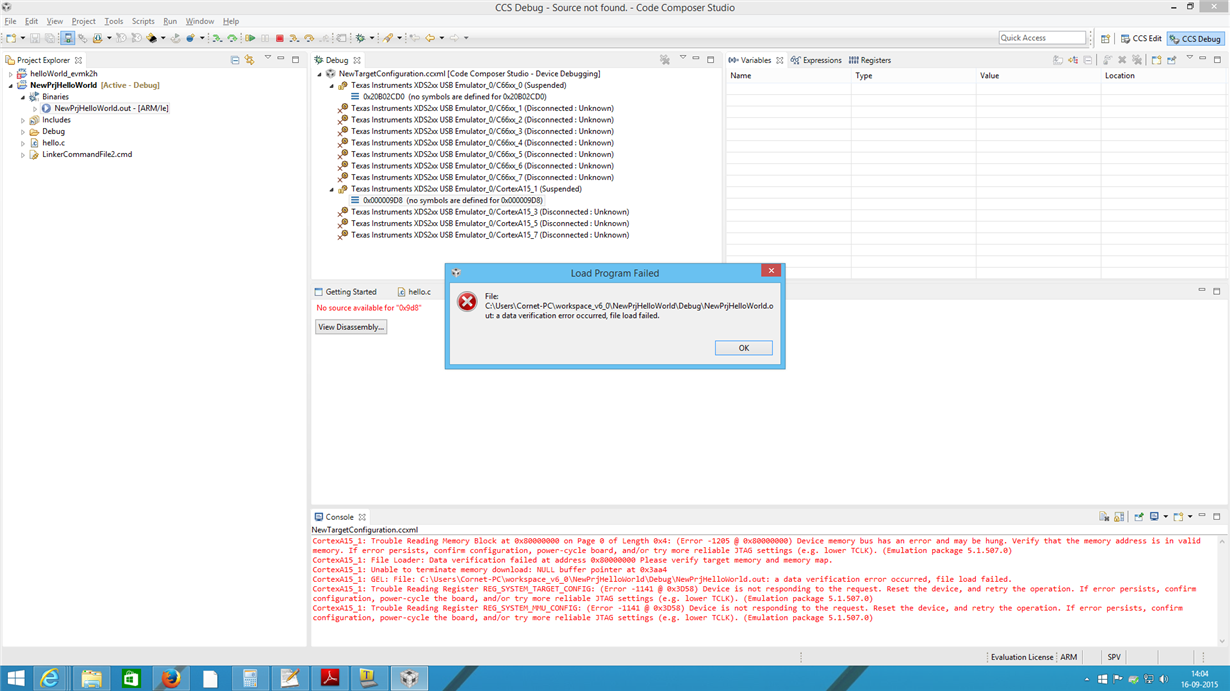

I'm using EVMK2H. I don't know where to get the Revision - On the box a sticker mentions (2P) REV: 40.

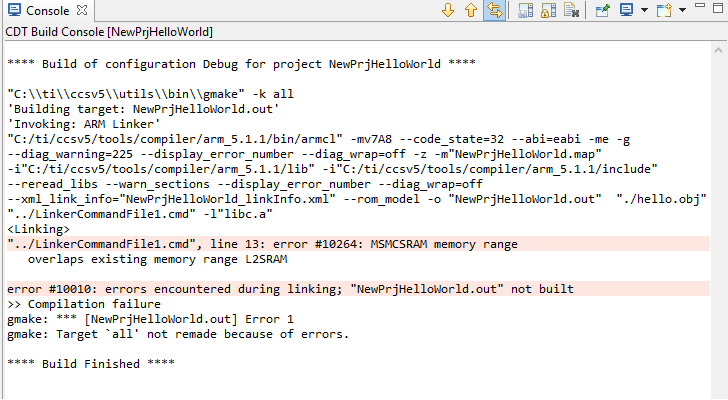

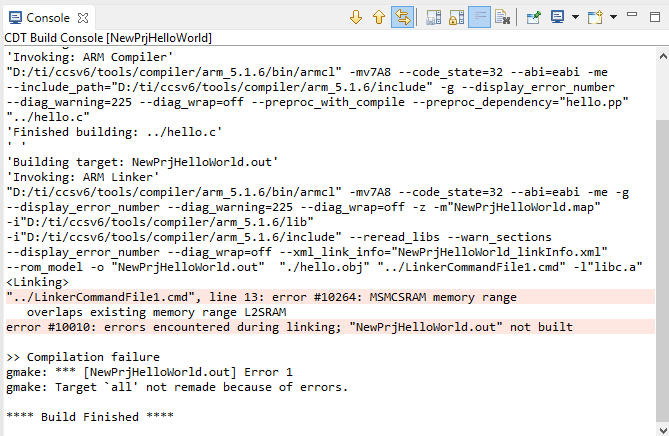

I have Code Composer Studio Version: 5.5.0.00077.

https://e2e.ti.com/support/dsp/c6000_multi-core_dsps/f/639/t/385728

I went through the responses in the link above.

- My board is in the No boot / JTAG DSP little endian boot mode

- I'm able to run on a DSP (C66xx_0) the sample project at "..\ti\mcsdk_bios_3_00_03_15\examples\ndk\helloWorld\evmk2h" mentioned by Shankari G in the link above.

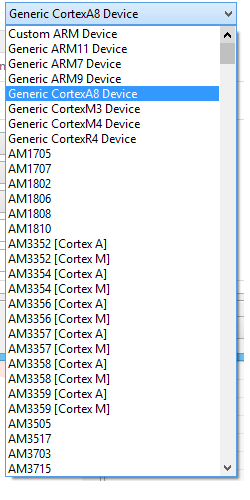

- Can someone tell me where a similar sample project exists for an ARM Cortex A15_1 ? The answer would be a path like "..\ti\mcsdk_bios_3_00_03_15\examples\ndk\helloWorld\evmk2h"

Thanks

Siddhartha