I try to switch ARM core wich works with SYS/BIOS into the privileged mode by instruction:

_call_swi(ARM_PRIV_MODE_KEY);

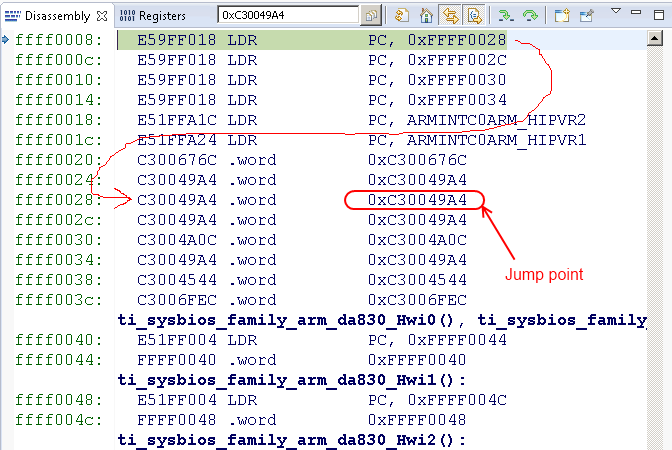

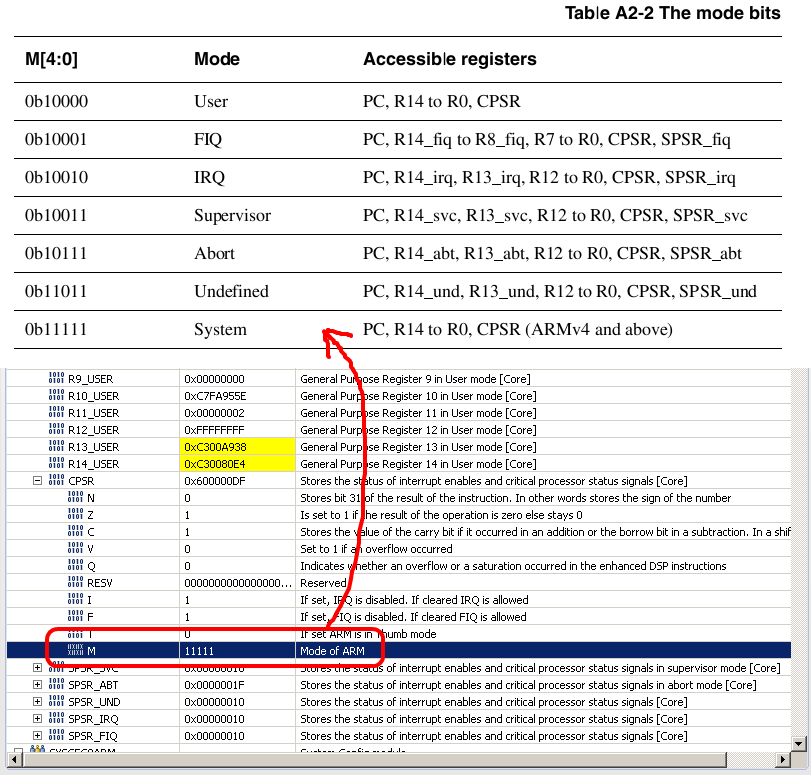

but it leads to falling into an exception handler. The problem is that there is an address of the subroutine of exception situated in the appropriate vector of SWI #0x50000. Why do it situated there? How to switch ARM core into the the privileged mode?

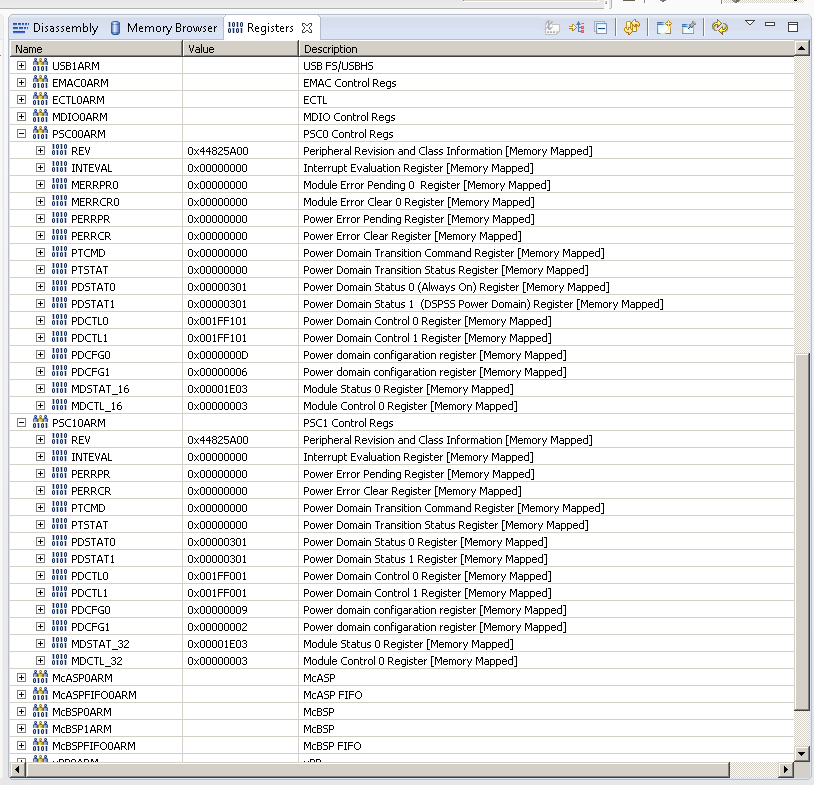

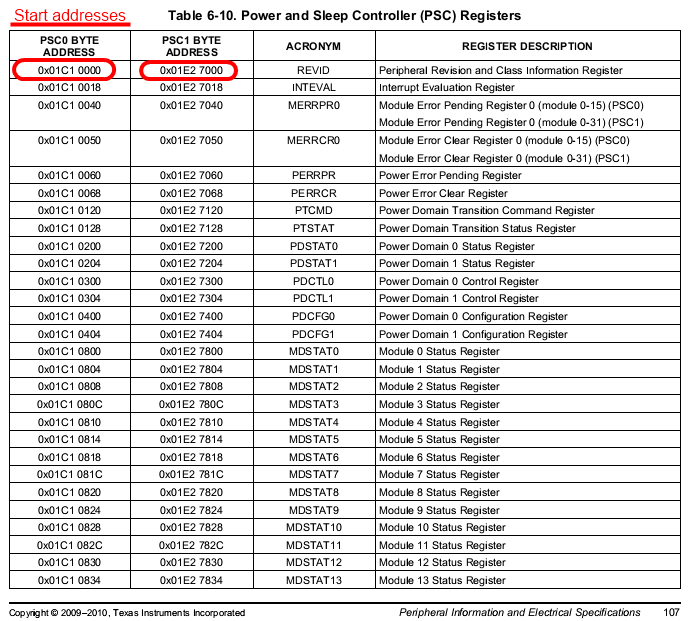

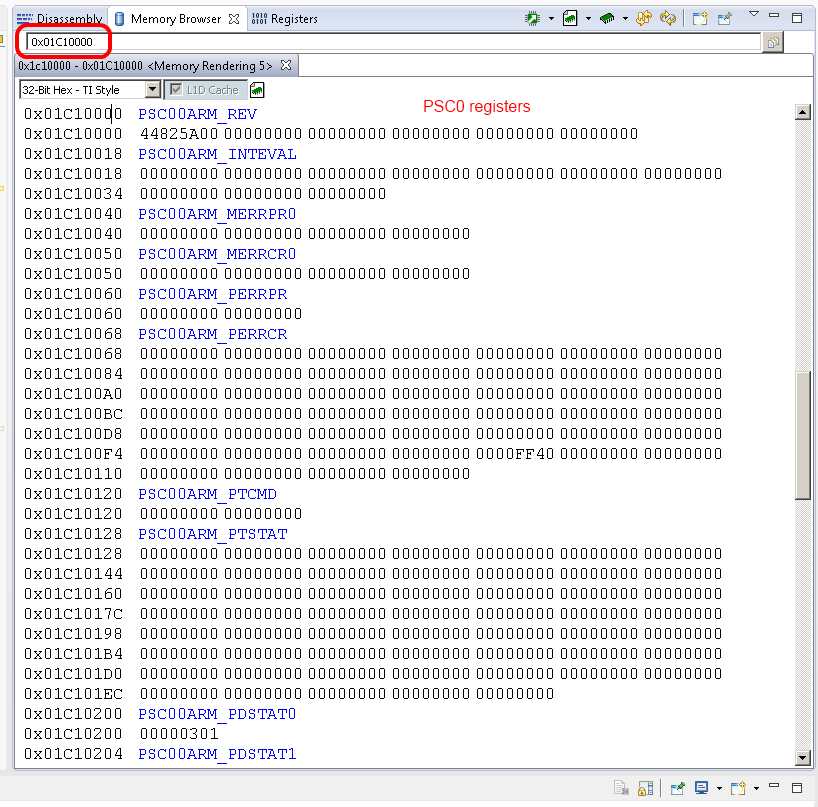

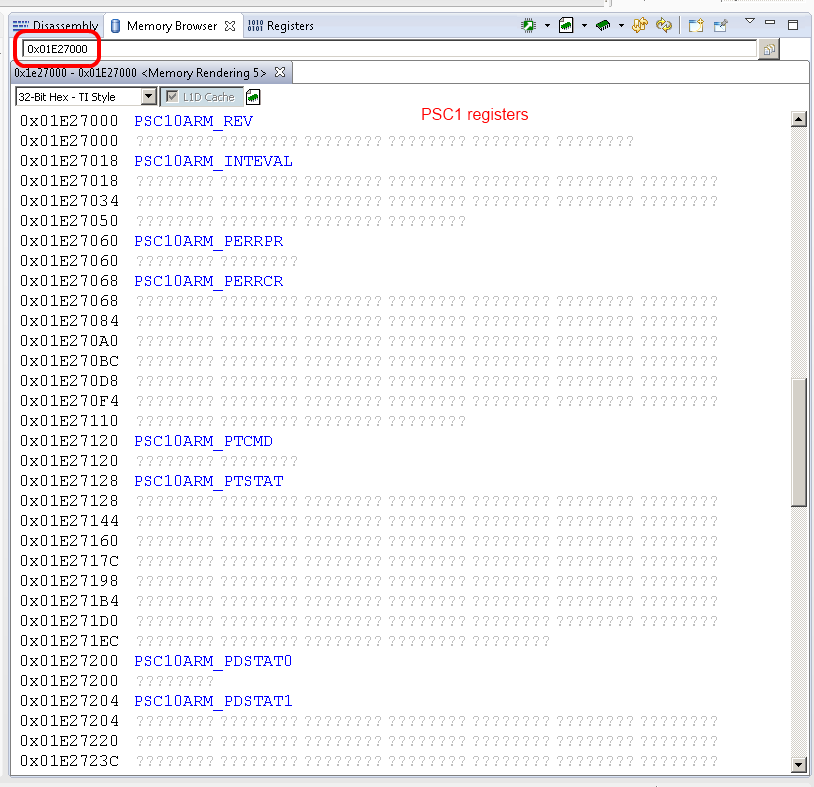

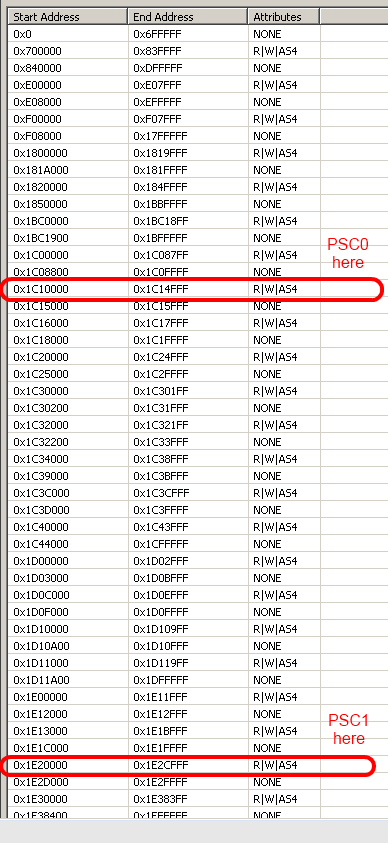

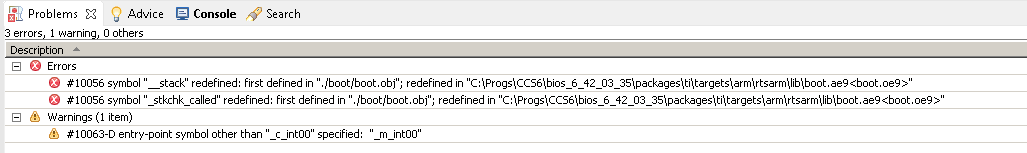

There are some screenshots which can help to understand the problem: