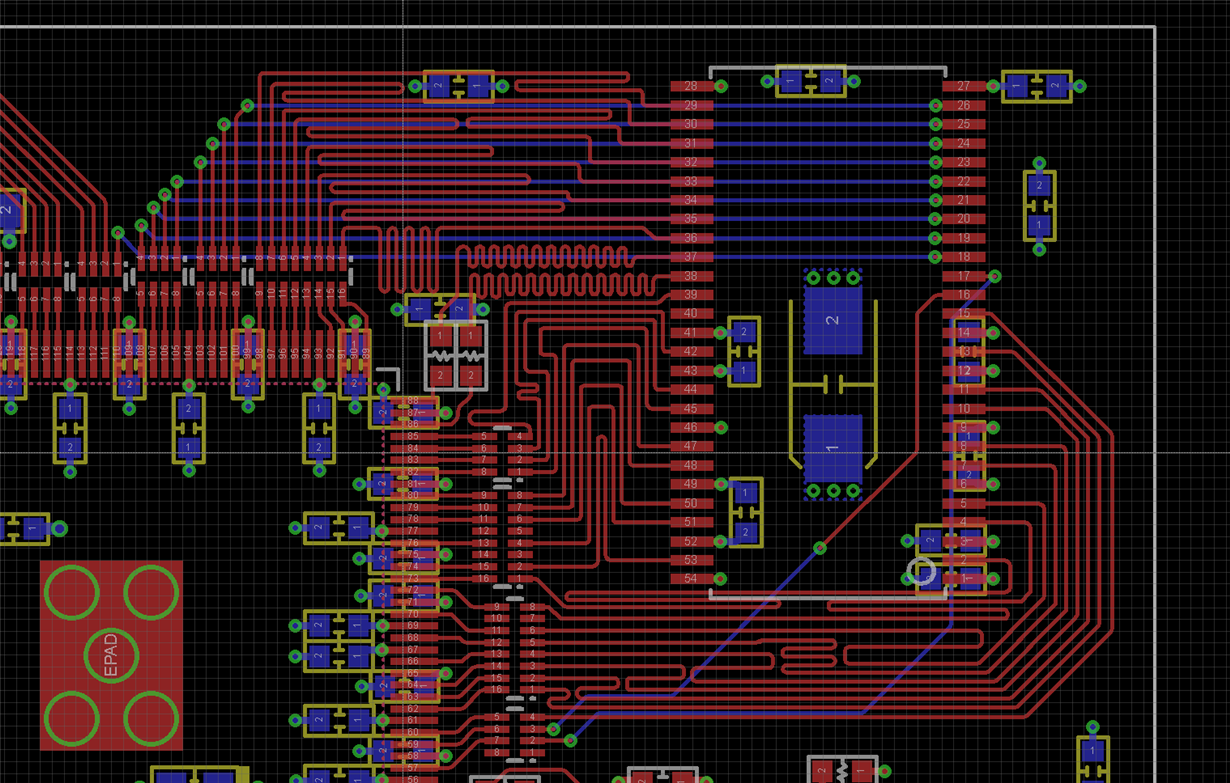

Using an SMD SDRAM on EMIFB, I have a feeling I blew the layout.

I matched all control signals within 0.5mm, DQM0/D0-7 within 0.2mm, DQM1/D8-15 within 0.2mm

But, the references I could find did not emphasize any relation between these three groups of signals, just match within the group.

CAS/RAS/CS0/A0-A12/BA0-BA1 = 37mm +/- 0.5mm

DQM0/D0-D7 17.5mm +/- 0.2mm

DQM1/D8-D15 42.5 +/- 0.2mm

WE/CKE/CLK 30mm +/- 0.5mm

1 x IS42S16800F-7TL SDRAM @128MHz/Latency=2

When I run, only the lower 8-bits gets read back from the SDRAM. The scope shows all lines with clean signal forms, though my setup is hard to do for multiple lines at once.

I ran the speed down to 60MHz and the same occurs.