Hi,

I have problem about C6455 PCI boot.

The problem is that PCI boot does not sometimes work.

C6455 continue to retry request for read access of the PCI configuration register from the PCI host.

I think that this phenomenon is very similar to the behavior that PCI bad state of errata(Adisory3.1.12[SPRZ234R]).

I will show the details of the board below:

- Circuit structure:

- C6455 Reset sequence:

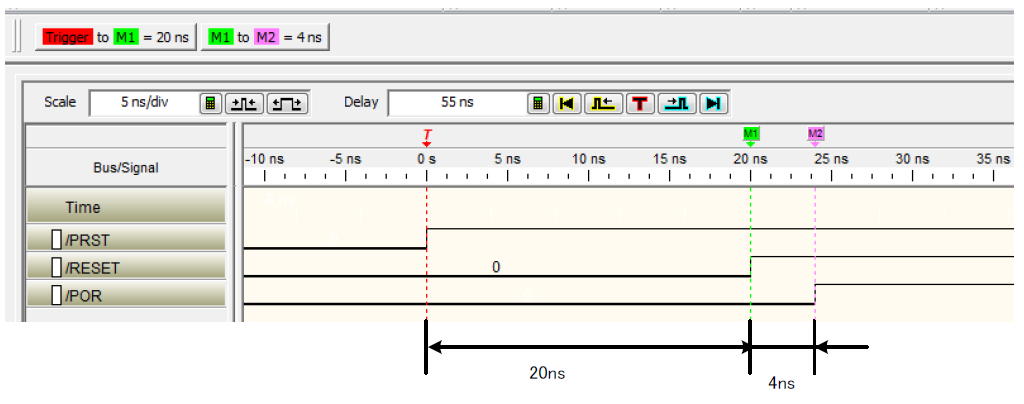

- Reset timing:

So, I have questions:

1. I think our circuit structure is equivalent to workaround (Fig. 6) of the errata.

but, would I have to /PRST and /RESET always High?

2. Our board has a short time(4ns) from /RESET deassert to /POR deassert,

Is this a likely a factor of the errata?

Best regards,

H.U