Hi,

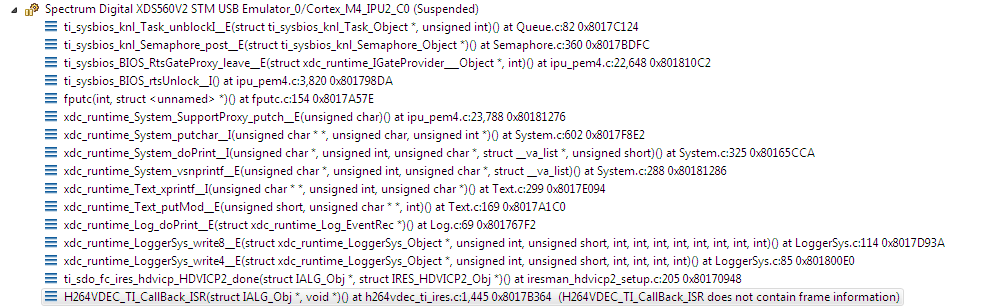

I have simple encoder and decoder application running on IPU2 (sysbios) directly. My application uses the TI HDVICP encoder and decoder. At times, I observe a crash inside the codec process call. I am running this application using CCS and have obtained the following stack trace.

[t=0x00000001:216346d7] ti.sdo.fc.ires.hdvicp2: [+E] ti_sdo_fc_ires_hdvicp_HDVICP2_w[t=0x00000001:21c3584d] ti.sdo.[t=0x00000001:21f682ed] ti.sysbios.family.arm.m3.Hwi: ERROR: line 1078: E_hardFault: FORCED

ti.sysbios.family.arm.m3.Hwi: line 1078: E_hardFault: FORCED

[t=0x00000001:22cce0b1] ti.sysbios.family.arm.m3.Hwi: ERROR: line 1155: E_busFault: PRECISERR: Immediate Bus Fault, exact addr known, address: f1016017

ti.sysbios.family.arm.m3.Hwi: line 1155: E_busFault: PRECISERR: Immediate Bus Fault, exact addr known, address: f1016017

Exception occurred in background thread at PC = 0x8017c124.

Core 0: Exception occurred in ThreadType_Swi.

Swi name: {unknown-instance-name}, handle: 0x80610678.

Swi stack base: 0x8060c570.

Swi stack size: 0x3000.

R0 = 0xf1a00204 R8 = 0x00000006

R1 = 0x00000000 R9 = 0x00000000

R2 = 0xf1016013 R10 = 0x00000000

R3 = 0x8060f80c R11 = 0xffffffff

R4 = 0x00000000 R12 = 0x00000010

R5 = 0x00000001 SP(R13) = 0x8060f2f8

R6 = 0x80610878 LR(R14) = 0x8017bdfd

R7 = 0x0000002e PC(R15) = 0x8017c124

PSR = 0x61000000

ICSR = 0x00435803

MMFSR = 0x00

BFSR = 0x82

UFSR = 0x0000

HFSR = 0x40000000

DFSR = 0x00000000

MMAR = 0xf1016017

BFAR = 0xf1016017

AFSR = 0x00000000

Terminating execution...

Apart from this, I have followed the instructions provided in the below link

processors.wiki.ti.com/.../BIOS_FAQs

I get a call trace as below

What could the issue be? Any inputs provided would be very valuable.

Thank you.

Regards,

Apoorva