Hi Team,

My customer is evaluating our AM5726 in field relay protection project. This project may potential be the high-voltage platform in future, so it’s important to us. Here comes a question about our reference design of AM5726 may need your kindly help answer. As you can see attached reference design from TI.

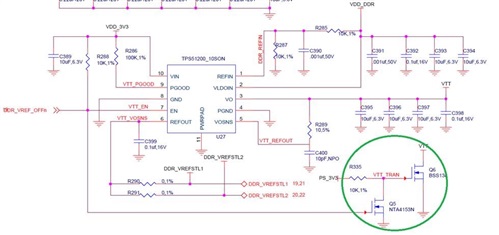

Customer has a question about using TPS51200 to provide power supply to DDR3’ VTT. They want to know below two MOSFET’s purpose and if they take away these two MOSFET, if these is any influence for the total system? Thanks a lot for your support!

Best regards,

Sulyn Zhang