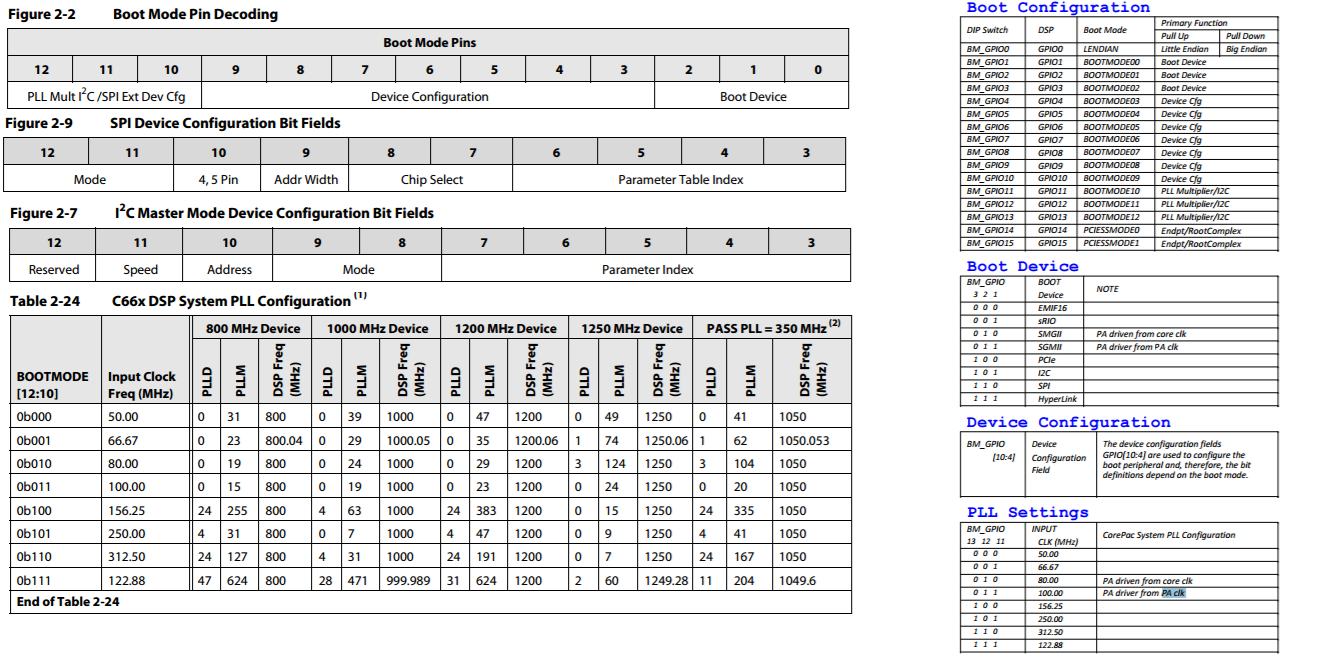

I am trying to set the bootmode of my C6678L EVM to "IBL NOR boot on image 0 (default))...this requires BM_GPIO11 to be "off", which is 1...The system boots fine. Now I want to keep the same boot mode but select the PA clk to be the code clock...this requires BM_GPIO[13, 12, 11] to be [0 1 0]...as you can see, BM_GPIO11 is conflicting with the boot mode I need...How to fix this?

Regards,

Murad